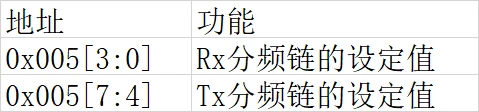

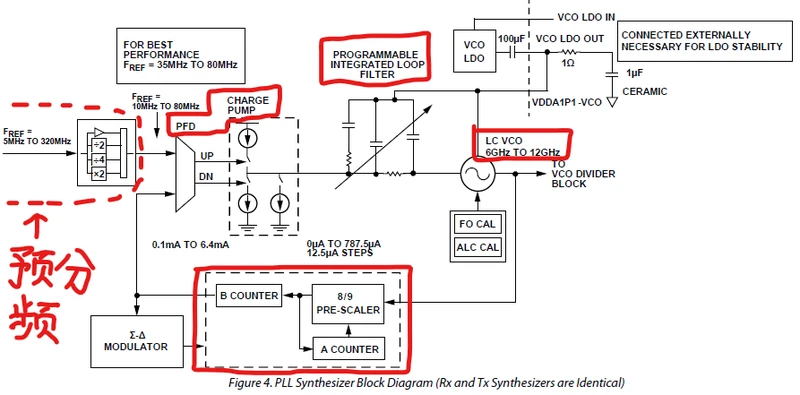

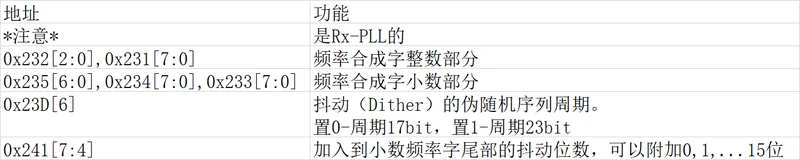

LO的产生过程如图:

各个模块都有高灵活性。

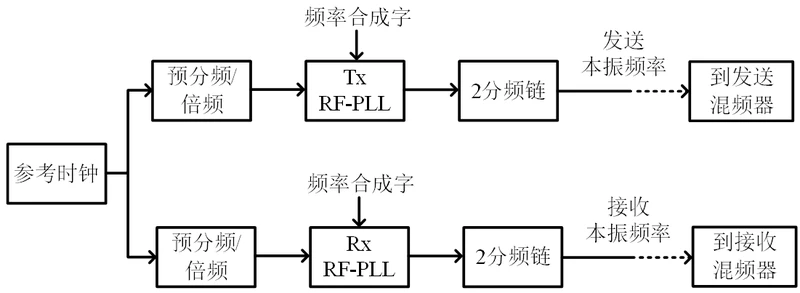

1、参考时钟即是AD9361全局参考时钟,可以是外接晶振的片上DCXO,或是外部输入的有驱动能力的时钟信号。根据FM-COMMS5的设计,参考时钟可以使用时钟Buffer + 40MHz晶振构成的参考频率源。

(1)关于DCXO的说明:DCXO即数控晶体振荡器,AD9361通过外接晶体和内部数控电容构建DCXO,外接晶体谐振频率需要在19MHz~50MHz 范围内。数控电容对于外接晶振的微调范围是±60 ppm。因此DCXO输出频率范围大致在20MHz~50MHz。

相关的寄存器:(说明:[4]表示这个寄存器的从低到高第4位,共有第0位到第8位;有些功能是多个寄存器联合表示)

(2)关于外部输入时钟的说明:外部输入时钟频率范围是5MHz~320MHz(推荐在19MHz~80MHz范围内),注意输入信号幅度不要超过1.3Vpp。

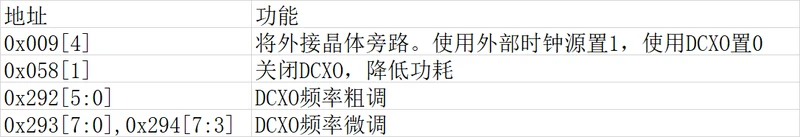

2、预分频/倍频可以对参考时钟进行预处理,即×2 ×1 ÷2 ÷4,这样的预处理可以完成时钟和后级鉴相器的隔离,同时调整频率使得PD正常工作。

相关的寄存器:

3、核心部件小数-N分频锁相环,包含频率合成经典结构:电流泵鉴相器、可编程环路滤波器,压控LC振荡器(VCO),小数分频器。

RF-PLL的结构图:

(1)鉴相器。正常工作前需要校准。其输出电流大小可以进行调节,范围0.1mA~6.4mA,步进100uA。

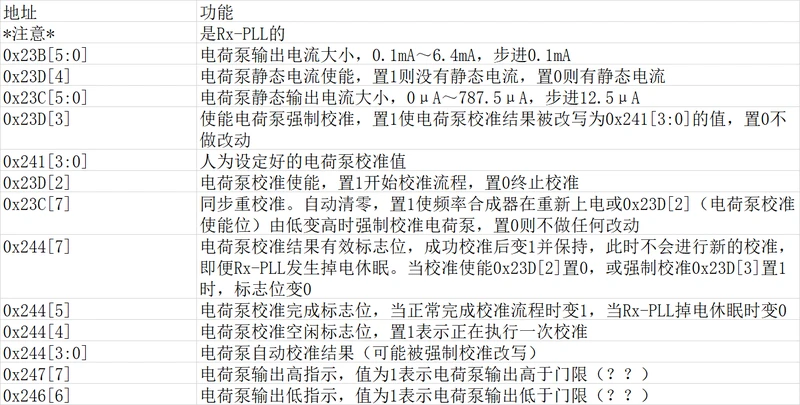

相关寄存器:(这些是Rx-PLL的电荷泵)

Tx-PLL的电荷泵寄存器地址是把第二个字加4,如0x23B变为0x27B,0x246变为0x286,etc.

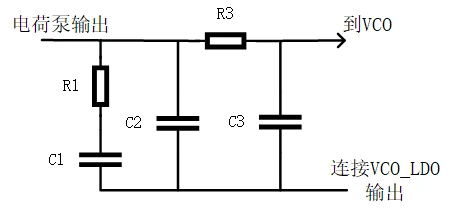

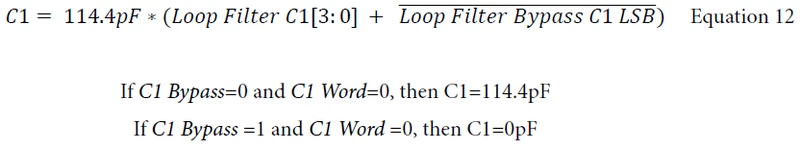

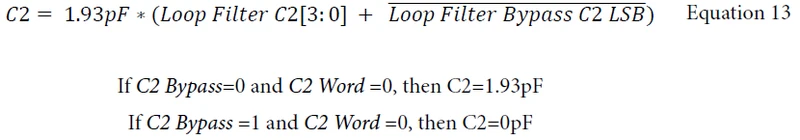

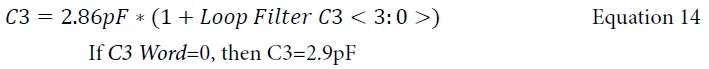

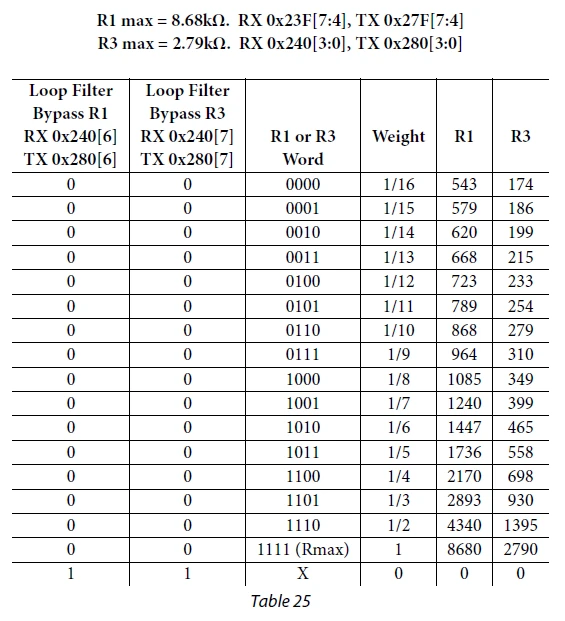

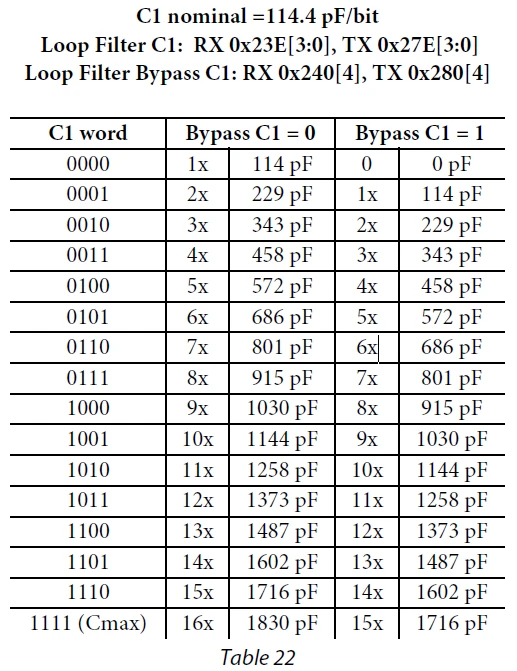

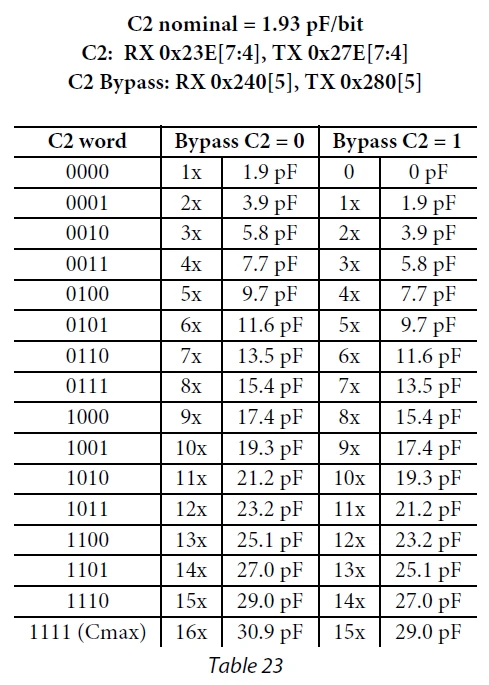

(2)环路滤波器。环路滤波器由电阻电容组成,每一个阻值容值都可以改变,字长4bit,4'b0000表示最小值,4'b1111表示最大值。除了电容C3,每一个元件都有使能位。电阻除能表示短路(0R),电容除能表示开路(0pF)。

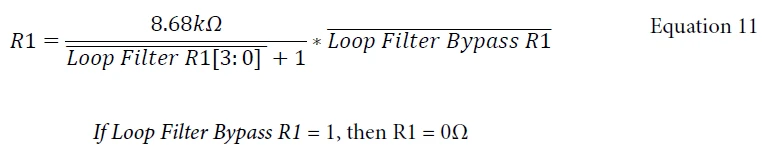

RC参数计算公式:(上方有横线表示位取反,Bypass表示使能位)

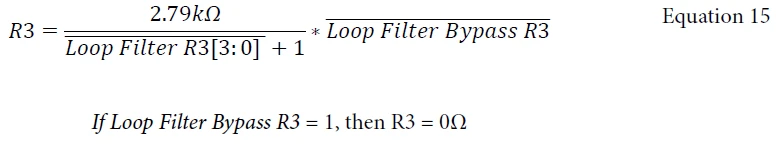

每个元件所有可能的标称值之表格:

为了获得良好的性能,ADI建议使用官方表格中的参数。

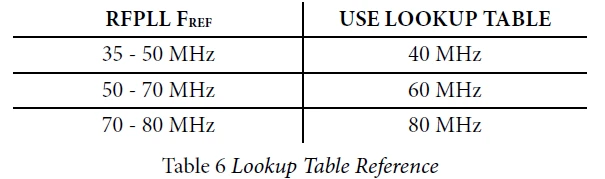

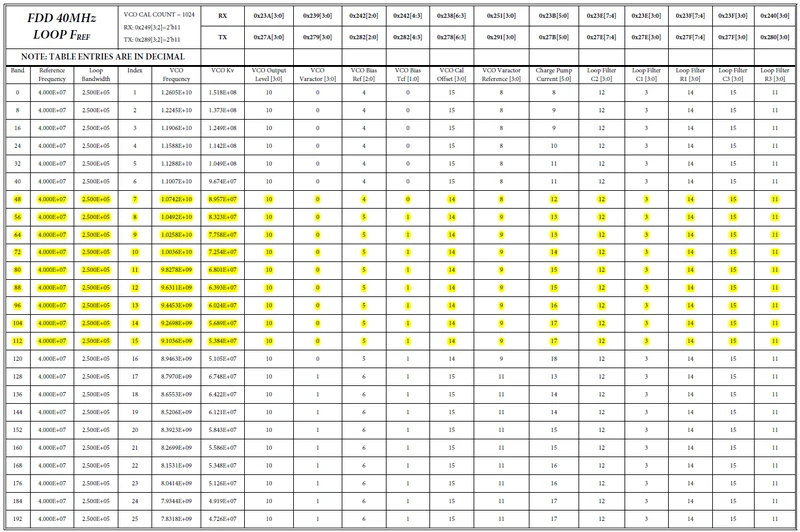

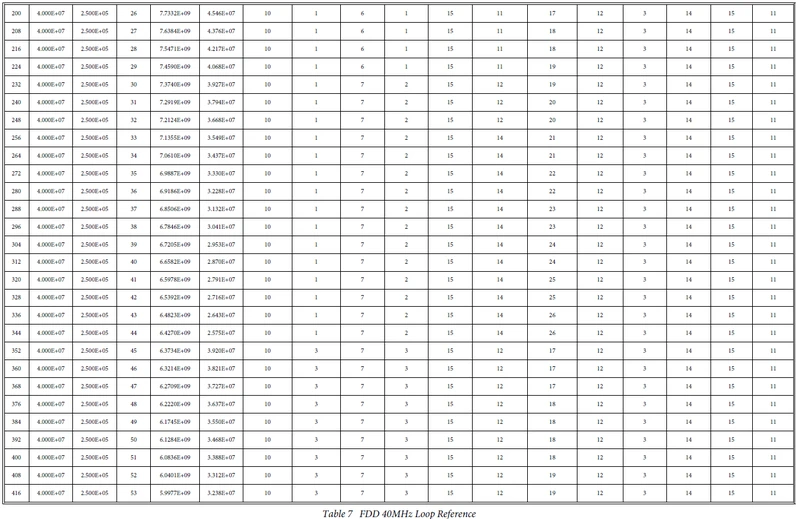

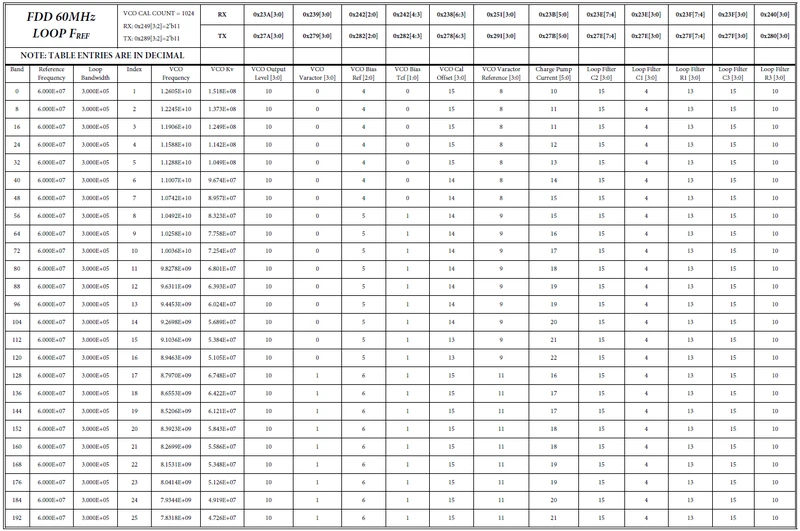

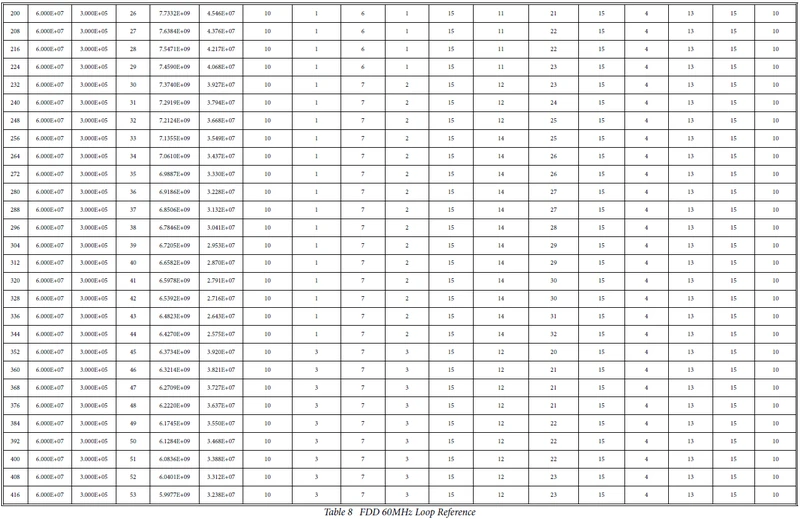

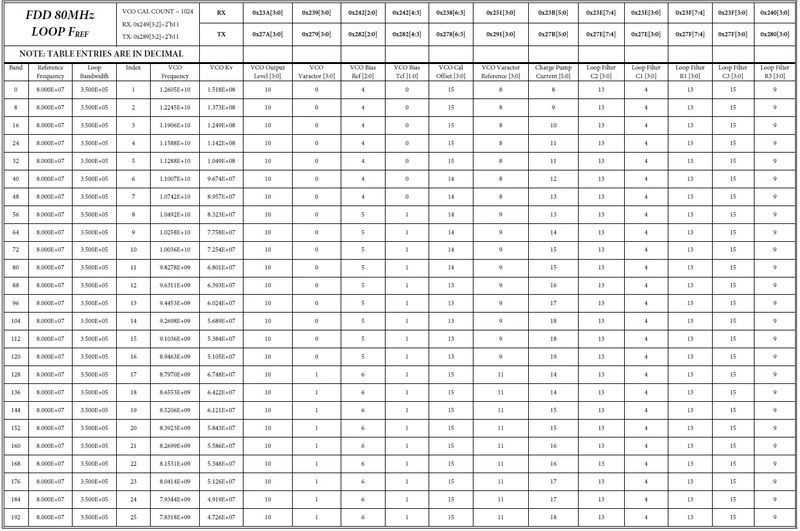

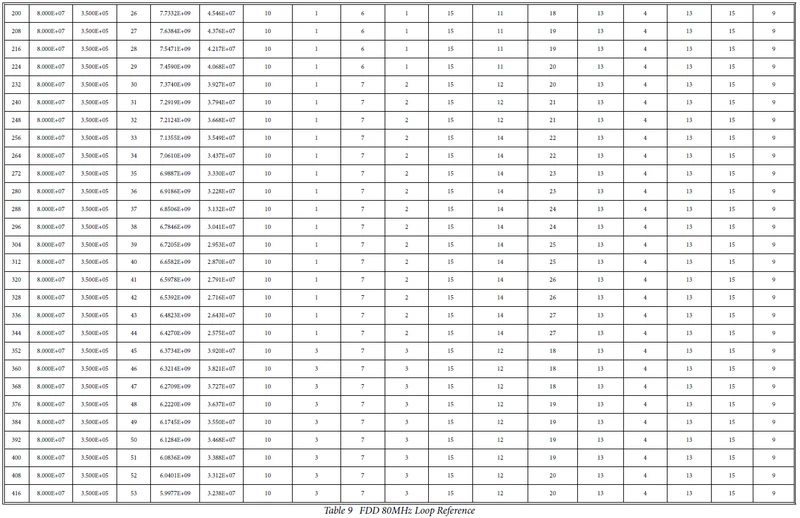

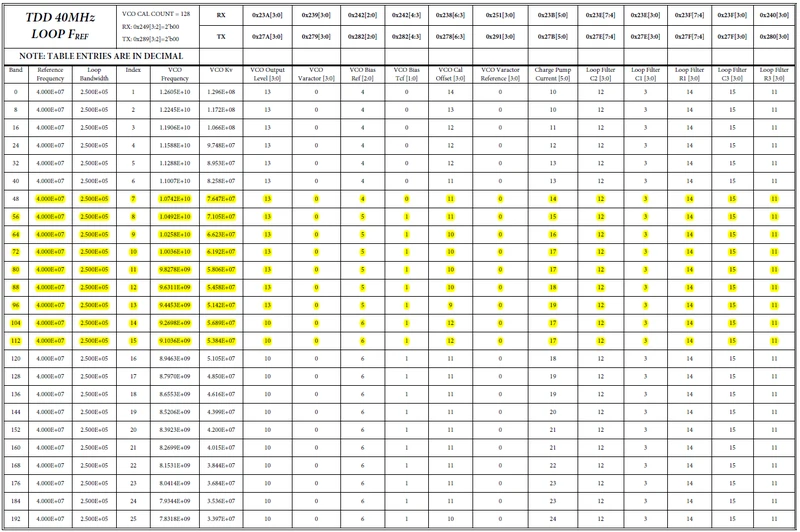

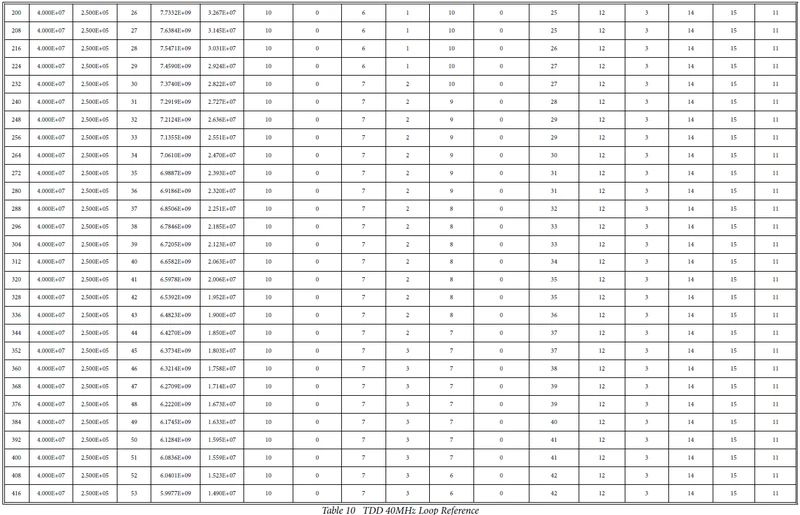

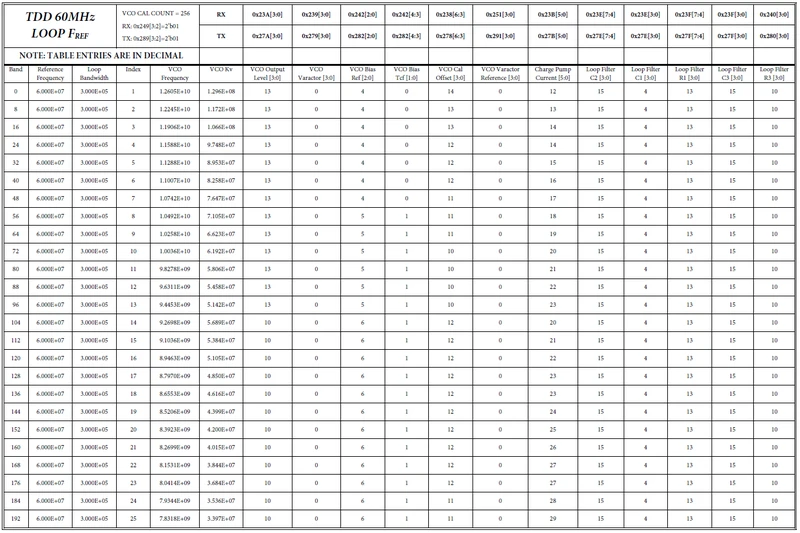

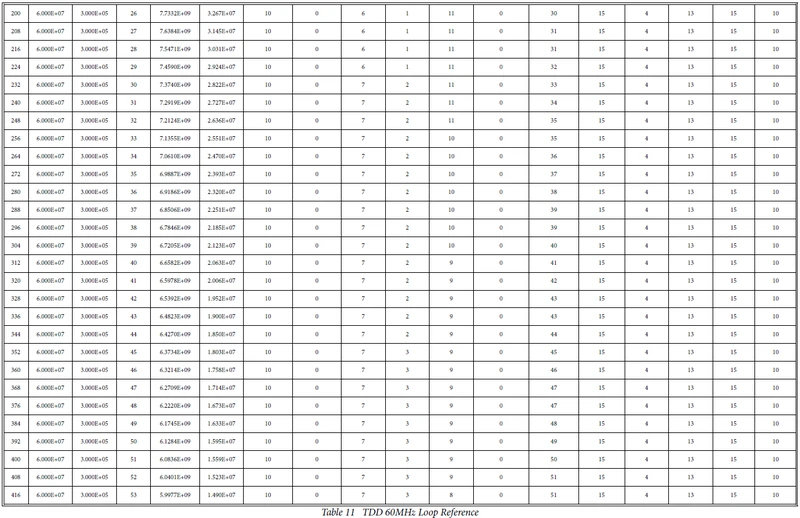

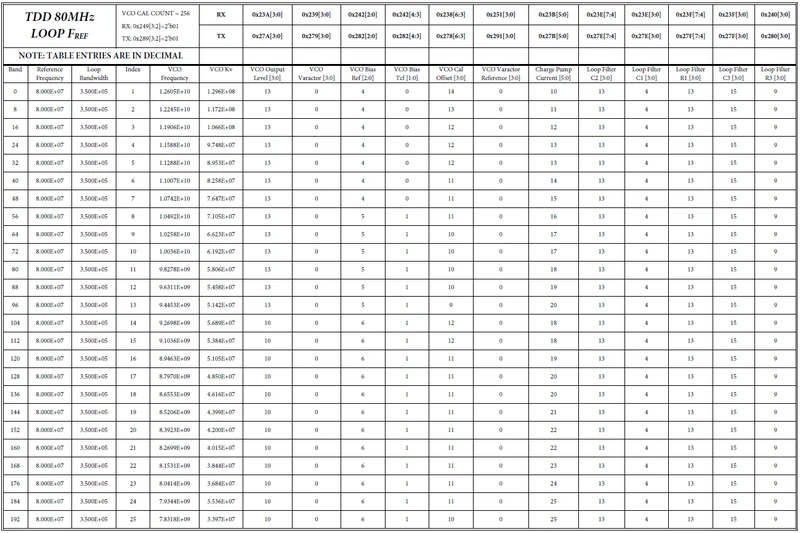

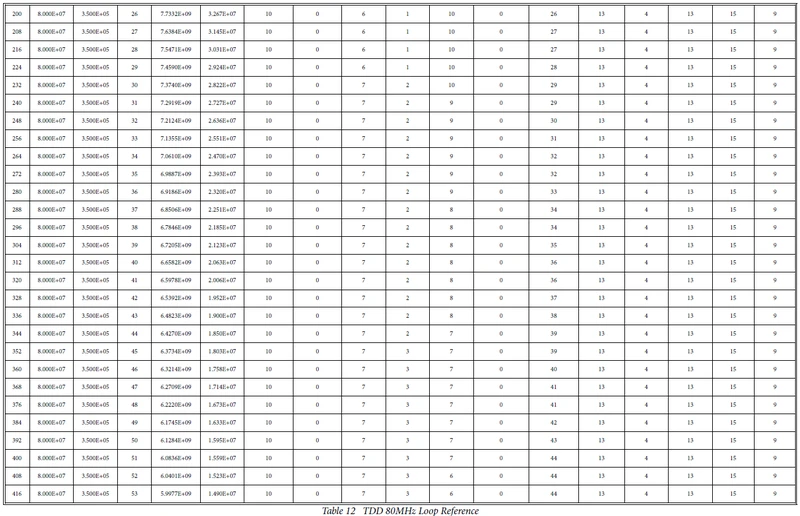

ADI给了6张表,分别是在TDD和FDD模式下,电荷泵输入的参考信号频率为40MHz,60MHz和80MHz时的配置。电荷泵实际输入参考信号频率与表的对应关系是:

先给出配置表:(寄存器的值以十进制表示)

表格使用方法:

[1] 根据工作模式(TDD/FDD)和鉴相器(即电荷泵)参考频率,从6个表中选择一个。

[2] 根据VCO的频率,选择合适的一行。先根据需要的本振频率,确定RF-PLL中VCO的频率。本振频率和VCO频率是“2^n”分频的关系,因此对本振频率进行累乘2,使其落在6GHz~12GHz,就得到期望的VCO工作频率Fd。Fd需要大于等于这一行中的VCO Frequency,并且小于上一行的VCO Frequency。该行对应了一组RF-PLL的配置值。

[3] 注意:每个表的表头有VCO CAL COUNT值,表示VCO频率校准计数长度,可能的值为128,256,512,1024.(详见VCO部分)在TDD模式下,VCO校准时间短,不进行温度补偿;在FDD模式下,VCO校准时间长,并且进行温度补偿。

相关寄存器:

(3)压控振荡器。VCO工作频率为6GHz~12GHz,正常工作之前需要向寄存器写好VCO的各种参数,然后执行VCO自动校准。

关于VCO校准的一点说明:

[1]以下3种行为会触发VCO自动校准:①当器件状态从WAIT变为ALERT;②TDD模式下,RF频率综合器从掉电休眠状态变为ALERT;③RF频率综合字最低位发生写入。

[2]VCO校准发生前,需要将RF-PLL环路内所有部件的参数设定写入好,包括电荷泵电流大小、环路滤波器参数、频率合成字等等。

[3]电荷泵校准必须在VCO校准之前进行。

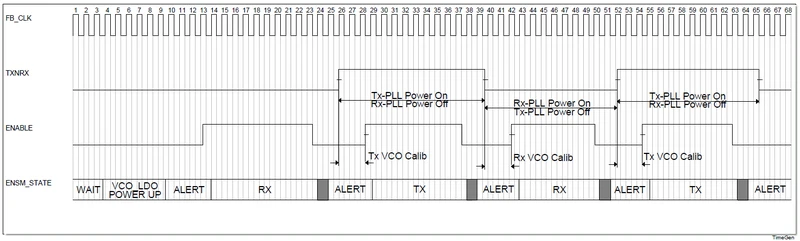

[4]TDD模式下,Tx RF-PLL和Rx RF-PLL会交替进行掉电休眠和校准。

当通过ENABLE和TXNRX进行收发切换,TXNRX直接控制了RF-PLL的工作状态:上电振荡还是掉电休眠。因此TXNRX的跳变只能在ALERT状态下发生,而不许在TX和RX状态下变化TXNRX。

在ALERT状态下,如果TXNRX信号从0变1,则Rx-PLL掉电休眠,Tx-PLL上电工作;如果TXNRX信号由1变0,则Rx-PLL上电工作,Tx-PLL掉电休眠。时序图标出了TDD模式下收发VCO进行校准的时机。

[5]当AD9361工作在FDD模式,需要更长的VCO校准时间,因为收发频率合成器都始终工作,需要精确的校准来对抗温度变化;在TDD模式,可以减少每次校准时间,因为设备收/发状态持续时间都较短,收发状态切换频繁,校准次数大大增加,温漂不明显。

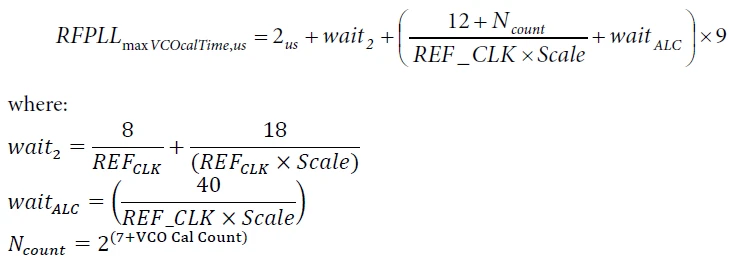

校准时间计算:

用MATLAB计算RF-VCO校准时间:

clc; clear; close all; %% Basic Param REF_CLK = 40; % MHz SCALE = 2; % Pre-scaler Factor VCO_CAL_COUNT = 3; % 0->127, 1->256, 2->512, 3->1024 %% Derived Param wait_2 = 8/REF_CLK + 18/(REF_CLK*SCALE); wait_alc = 40/(REF_CLK*SCALE); N_count = 2^(7+VCO_CAL_COUNT); %% max_calib_time_us = 2 + wait_2 + 9*((12+N_count)/(REF_CLK*SCALE) + wait_alc); disp(['max RF-PLL Calib Time = ', num2str(max_calib_time_us), 'us']);

[6]VCO校准可以被关闭。

[7]校准完成标志位是:Rx PLL Lock @ 0x247[1]和Tx PLL Lock @ 0x287[1]。

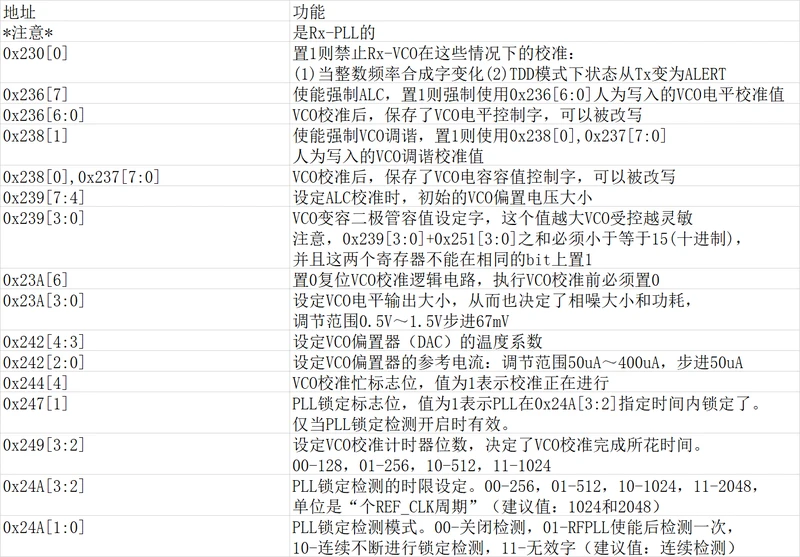

相关寄存器:

(4)小数分频器。分频器决定VCO稳定时的输出频率。

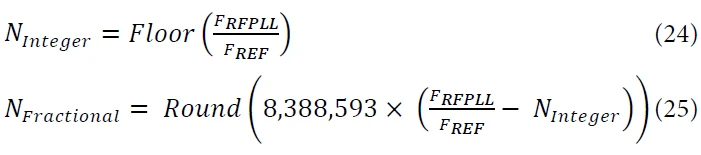

频率合成字的整数和小数部分计算方法:

其中F_REF是RF-PLL的输入参考频率,和上面的REF_CLK是一回事。F_RFPLL是VCO的输出频率(注意这个频率范围是6GHz~12GHz)。

N_Integer是11bit的整数部分,N_Fractional是23bit的小数部分。(8388593接近2^23=8388608)

小数分频器中使用抖动(Dither)技术,使得频率字小数部分的末位伪随机化,来降低杂散。

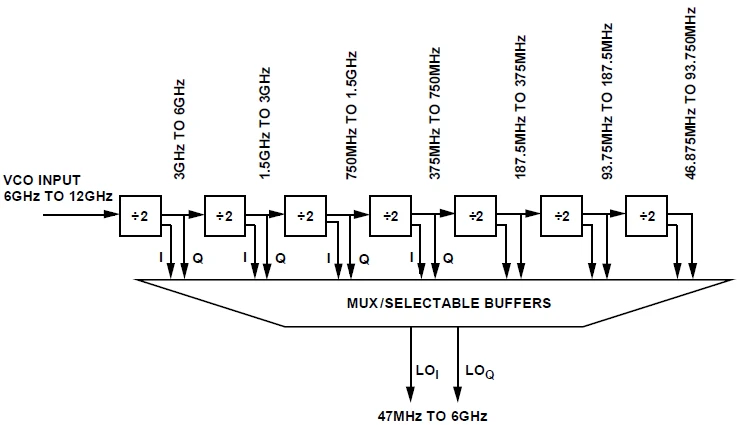

相关寄存器:(Tx对应的寄存器地址是Rx地址+0x040,如Rx的0x231对应Tx的0x271)

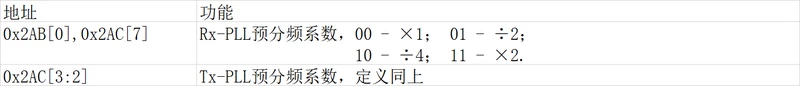

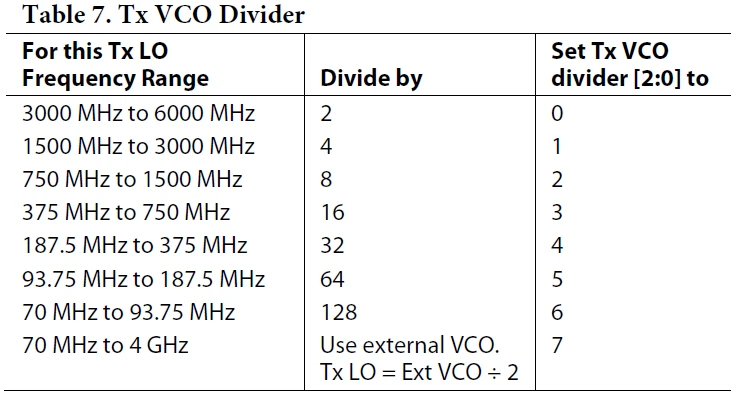

4、2分频链。VCO输出经过2分频得到本振信号。

分频器还包含了正交移相器。

分频系数是由期望的本振频率指定的。关系如下:

分频值和寄存器设定值的关系是:

![]()

相关寄存器: