前言:

这篇日志是我记录自己做CPU时候的工作进度以及思考,灵感,问题,里面记录了很多的BUG,如果遇到了一些BUG可以来这篇日志里面查找

日志的后半部分我认为是比较有营养的

这篇日志非常的长,原版我是记录在一个WORD文档里面的,这个文档可以在我发布的CPU工程文件里面找到,文档里面文字有,加粗,字体颜色,更方便阅读

完整的CPU工程文件可以在下方链接下载.无需花费积分哦

//download.csdn.net/download/qq_43536068/12037172

标题关于控制信号的整理可以查看我的另一篇博客

https://blog.csdn.net/qq_43536068/article/details/103590023?utm_source=app

12/11修复了PC寄存器的问题,就是输入一个地址后只是当前那个周期输出这个addr,后续又变回来原先的addr

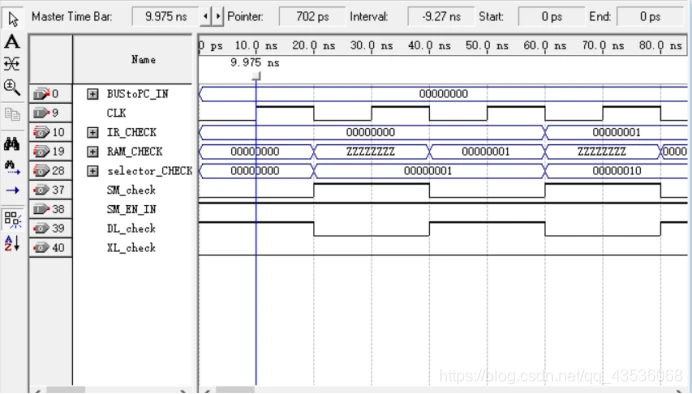

Ram的性质是获取上升沿前一瞬间的控制信号

取指令联合调试完成

Ram正常在上升沿读出,IR正常在下降沿写入

12/12突然想到,我应该一边联合调试各个部件,一边用自己弄的那种输入来检查自己的控制信号产生逻辑是否是正确的

联合调试的时候,是从”事件”的视角去看待某个事件(比如取指令)的控制信号都是什么,再与单个控制信号进行对照就OK了

另外,我决定直接把SM加个反相器就连接到LD_IR上面,这样子简单不易错

发现一个错误,RAM的/CS口是专业的”低电平有效”,看来cs需要直接连接到时钟,否则会造成ram在不恰当的时间向BUS输出了数据,或者从BUS读入了数据

等等…好像ram这个元件的clk输入口我已经连接了…那就不会错了

对未来的提醒:目前,c,z尚未用到,但是这两个口决定能否输出jmp和jz这二个指令,或许…这两个口可以加在指令译码器?

修正了控制信号产生逻辑的一个重大bug之后,我成功让取指令周期自动跑起来了

但是好像有点不对,因为我预期的ram是”上升沿读出”的,但是很明显,现在的ram是”下降沿就输出了数据,并且保持一个周期”这不是我想要的(虽然似乎没有什么问题)

经过反复验证,我认为是ram元件本身出了问题

但是我又去我原本的ram那里进行了ram单个元件的测试,发现是有上升沿写入的性质的,但是到了我的cpu里面就失去了这个性质…

2019-12-14开始制作mov指令

先做MOVA

MOVA R1,R2是三个寄存器之间的互相移动,把数据从R1移动到R2

执行周期与此指令相关的控制信号

移位逻辑

F-BUS 1

FL-BUG 0

FR-BUS 0

ALU

S[3…0] 1111

M 0

通用寄存器组

RAA 不固定

RWBA 不固定

/WE 0

**{BUG}**发现了控制信号产生逻辑里面的一个bug,

RAA <= IR(1 downto 0);

RWBA <= IR(3 downto 2);

之前我一直以为RAA是[3 downto 2]

啊啊啊啊,这个bug不仅在控制信号产生逻辑里面有,在指令译码器里面也有啊啊啊啊啊,我死了,稍后再做修改

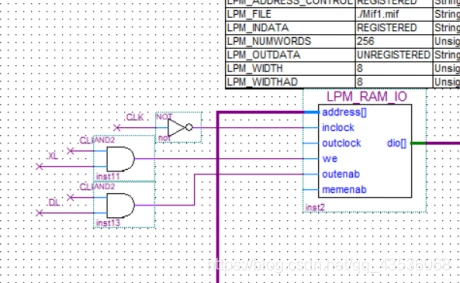

我猛然发现,原来RAM的CS和CLK不是一个口!!!

我在增加了两个骚气的与门之后RAM能在timing仿真下按照我的意愿工作了

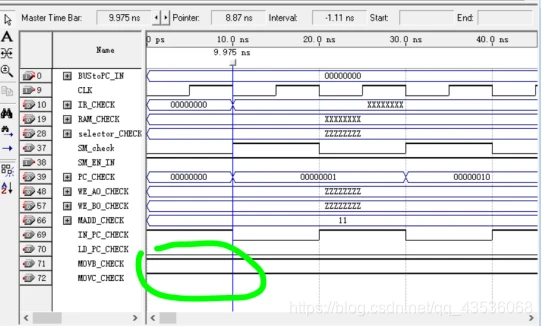

为什么我一把指令译码器和控制信号产生逻辑连接在一起,就tm的连取指令的执行都错误了!!!我仔细排查了一下,问题出似乎在MADD那里,因为selector输出”ZZZZZZZZ",所以我又排查了MADD的控制信号产生逻辑,似乎没问题…那么…就一定是指令译码器有问题了

我的猜测被证实了,果然’是指令译码器出现了问题

在我de掉指令译码器的错误之后,”取指令”的操作变得更加诡异了

但是我似乎发现了什么

**{BUG}*