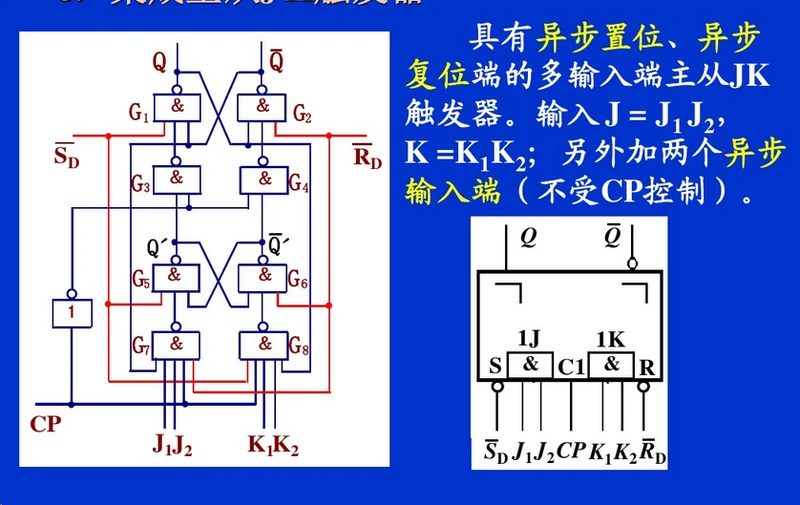

(一)T触发器(最简单)

-

什么是T触发器:

在数字电路中,凡在CP时钟脉冲控制下,根据输入信号T取值的不同,具有保持和翻转功能的电路,即当T=0时能保持状态不变,T=1时一定翻转的电路,都称为T触发器。

输入端2个:T 、CLK

输出端2个:Q、Q’(Q’是Q逆的意思,与Q状态永远相反) -

逻辑符号

-

T触发器功能:

T=0时,CLK输入,Q保持不变

T=1时,CLK输入,Q翻转. -

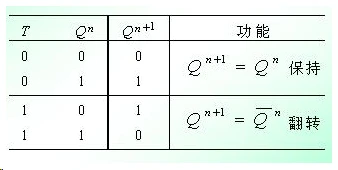

T触发器的特性方程

Q * = T Q ’ +T ’ Q -

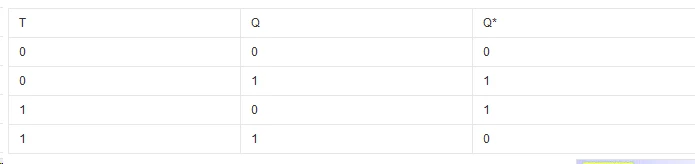

T触发器的特性表

-

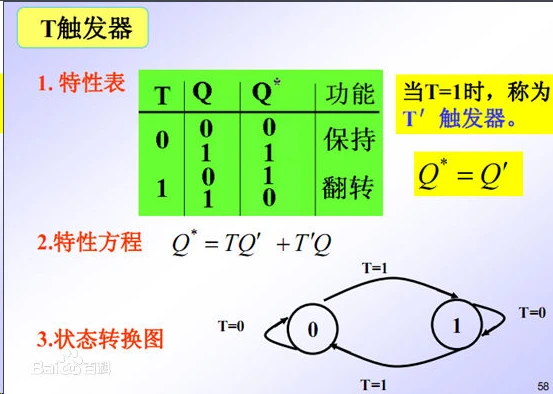

波形图

这是CLK时钟下降沿触发的T触发器的波形图

波形图分析:(对照特性表)

一、当clk产生第1个下降沿时:看T的高低电平,由特性表可知,当T为高(1)时,Q状态翻转,此时Q由0变为1,(Q‘是Q逆的意思,也就是说Q’的状态永远和Q相反)

二、当clk产生第2个下降沿时:看T的高低电平,由特性表可知,当T为低(0)时,Q状态保持,此时Q保持高电平1

三、当clk产生第2个下降沿时:自己分析

…

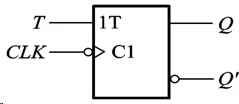

(二)D触发器

-

什么是D触发器

D触发器是一个具有记忆功能的,具有两个稳定状态的信息存储器件,是构成多种时序电路的最基本逻辑单元,也是数字逻辑电路中一种重要的单元电路。

普通的电路,以及常规的逻辑门都有一个共性,那就是输出直接依赖于输入,当输入消失的时候,输入也跟着不存在了。当输入撤销之后,D触发器输出依然能够维持。这就是说,D触发器具有记忆能力。

触发器具有两个稳定状态,即"0"和"1",在一定的外界信号作用下,可以从一个稳定状态翻转到另一个稳定状态。

触发器有集成触发器和门电路组成的触发器。触发方式有电平触发和边沿触发两种。

输入端2个:D、C(CLK)

输出端2个:Q、Q’ -

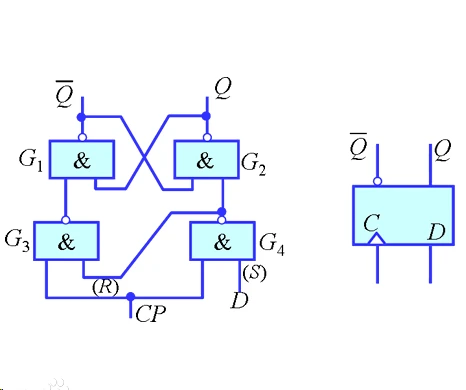

逻辑符号和内部图

-

功能

(1)当触发方式为上升沿触发时:

只有当CLK产生上升沿的时候,输出端(Q)才会根据输入端D的状态变化状态,D为1时,Q为1,D为0时,Q为0;

当CLK不是上升沿的时候(高电平,低电平,下降沿),Q状态是保持不变的(不论D电平是什么样的)。

(2)当触发方式是下降沿触发时,只有CLK产生下降沿的时候,Q才会根据D状态变化 -

特性方程

Q=D -

特性表

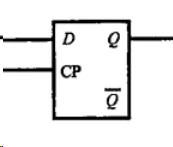

6.时序图

此图为上升沿触发方式

分析:

第一个上升沿:D为0,Q为0;

第二个上升沿:D为1,此时Q变化为1;(注意:在第一二个上升沿之间,虽然D产生了变化,但是Q保持之前状态不变)

后面自己分析

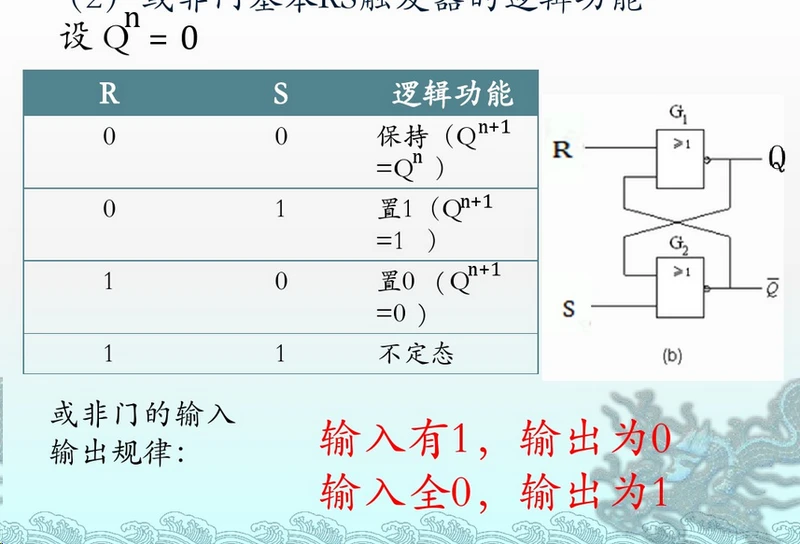

(三)RS触发器

1.什么是RS触发器:

RS触发器,也有人叫它RS锁存器,用于实现“记忆”电路状态/数据功能的东西 。问过学过数电的人,有说触发器和锁存器对信号的触发方式虽然不同但是工作原理其实一样的,触发器是边沿变化,锁存器是电平变化…但是两者的逻辑图和原理都一样的,所以在这就不做区分了。

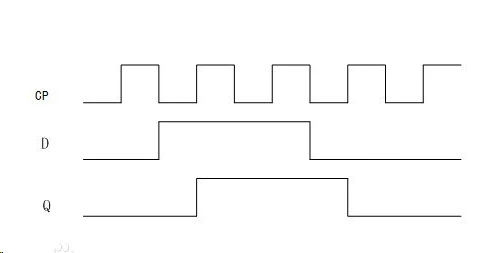

-

符号

-

功能分析

分析

R=0, S=1:无论触发器原来处于何种状态,由于S=1,则Q=1,Q非=0,触发器处于“1”态(或称置位状态)。触发器的状态是由S所决定的,称S为直接置位端。

R=1, S=0:无论触发器原来处于何种状态,由于R=1,则Q=0,Q非=1,触发器处于“0”态(或称复位状态)。触发器的状态是由R所决定的,称R为直接复位端。

R=0,S=0:触发器维持原来状态不变。

R=1,S=1:此时无法确定触发器的状态。一般这是不允许的,因此触发器的输入端S、R不能同时为0。 -

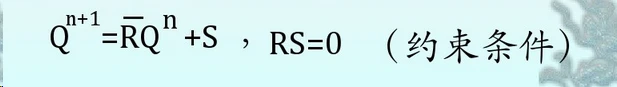

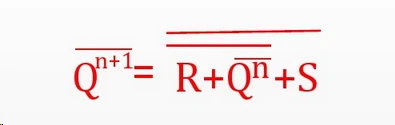

特性方程

5.特性表

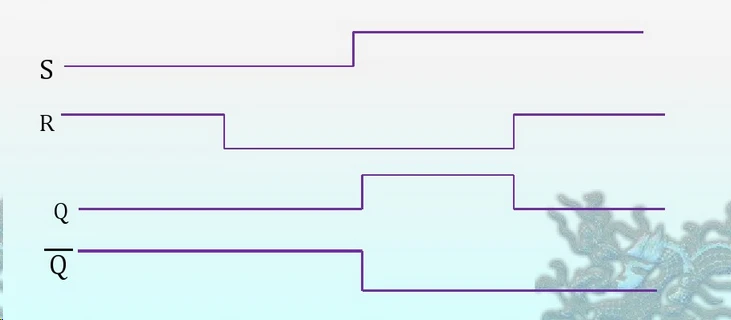

6. 波形图

6. 波形图

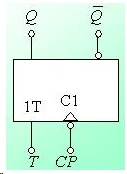

(四)JK触发器

https://wenku.baidu.com/view/a973c446be1e650e52ea997d.html

-

什么是JK触发器

JK触发器是数字电路触发器中的一种基本电路单元。JK触发器具有置0、置1、保持和翻转功能,在各类集成触发器中,JK触发器的功能最为齐全。在实际应用中,它不仅有很强的通用性,而且能灵活地转换其他类型的触发器。由JK触发器可以构成D触发器和T触发器。 -

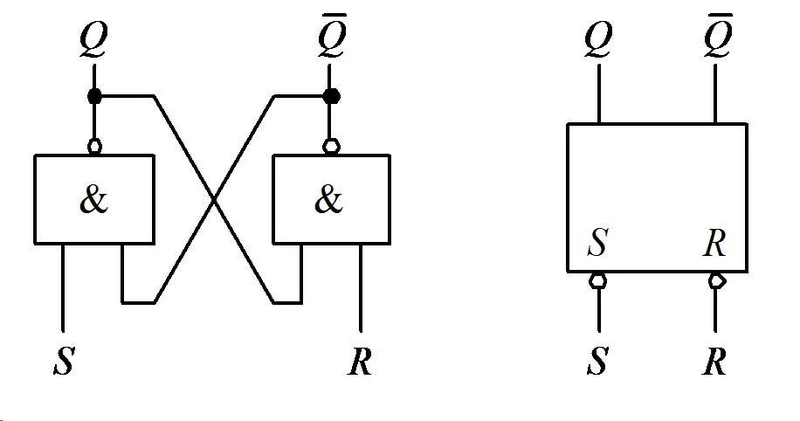

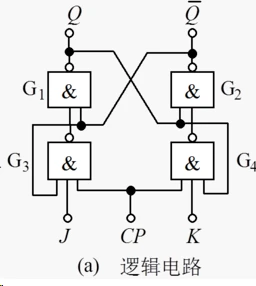

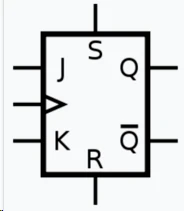

符号

3.功能分析

主从JK 触发器是在主从RS触发器的基础上组成的,由上面的电路可得到S=JQ,R=KQ。代入主从RS触发器的特征方程得到:

J=1,K=0时,Qn+1=1;

J=0,K=1时,Qn+1=0;

J=K=0时,Qn+1=Qn;

J=K=1时,Qn+1=~Qn -

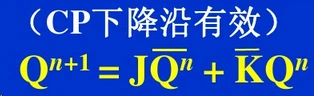

特性方程

5. 特性表

5. 特性表

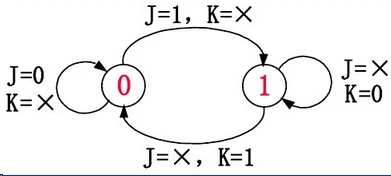

6. 状态转换图

6. 状态转换图

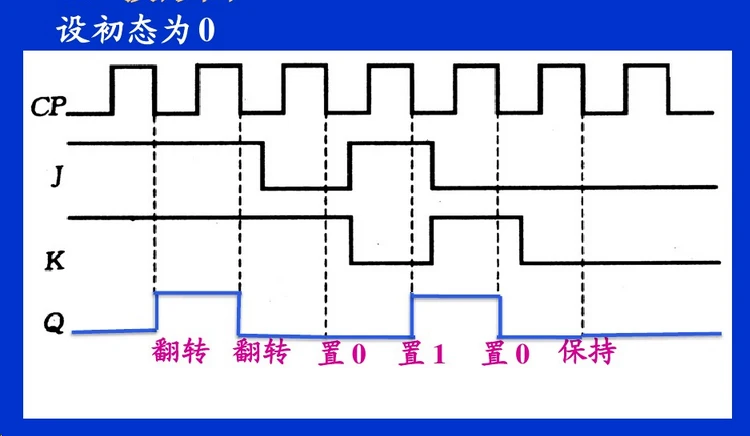

7 波形图

7 波形图

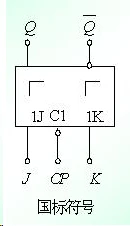

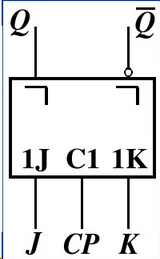

8. 集成主从JK触发器(难啊)

8. 集成主从JK触发器(难啊)