目录

一、AXI协议基础

1.1读写通道的基本架构图

1.2猝发操作举例

1.3传输顺序

二、各个通道中的信号描述

2.1全局信号

2.2写地址通道信号

2.3写数据通道信号

2.4写响应通道信号

2.5读地址通道信号

2.6读数据通道

三、通道握手

3.1单一信息传输时的握手过程

3.2不同通道之间的信号握手关系

四、寻址项

五、数据总线

5.1字节开关WSTRB

5.2窄带传输

六、非对齐传输

七、其他

一、AXI协议基础

AMBA AXI协议主要用于实现高性能、高频率系统的计算,能向下兼容AHB协议和APB协议。它具有以下几个特点:(1)五个分离的地址、数据通道;(2)具有字节开关,可实现非对齐的数据传输; (3)猝发地址由初始地址发起等等。

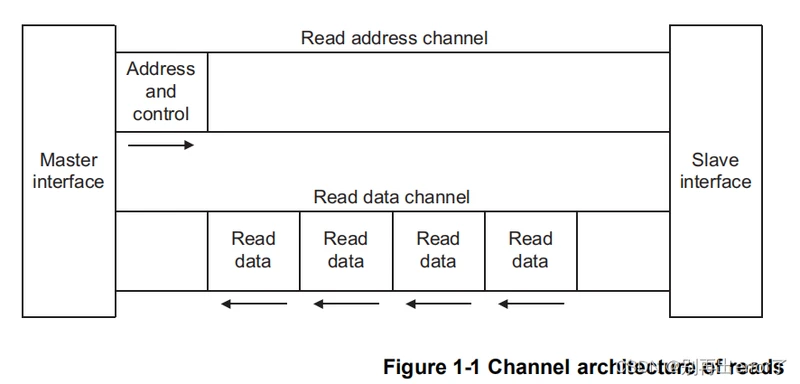

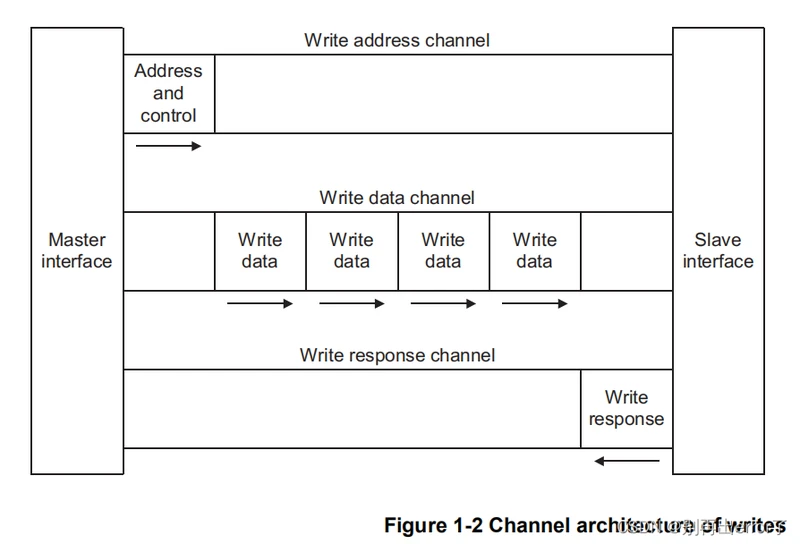

AXI最鲜明的特征是有五个独立的通道,分别是读数据、读地址、写数据、写地址、写响应通道。每次数据传输都具有地址和控制信息,通过地址通道传输; 在写操作中多了一个写响应通道,slave可以通过此通到向master发送一个写数据已经完成的反馈。

1.1读写通道的基本架构图

如图可知,地址、控制信息等通过地址通道发送,数据流方向都是从master到slave,即动作都由master发起;读写数据通过数据通道传输,写数据时数据流方向是从master向salve,即master向slave中写入数据,读数据时数据流方向从slave到master,即master读出slave中的数据;写响应通道传输写操作完成的反馈,通过写响应通道传输,方向是从slave到master。

1.2猝发操作举例

猝发burst是AXI总线协议的核心,猝发传输也叫突发传输,特点在于,一个burst可传输多个数据包(由len参数决定),且每次传输只需要传输一个初始基地址(addr),在slave端会自动为后续数据包的地址进行计算(多种计算方式)。在具体的传输过程中还牵扯一些乱序传输、字节通道等问题,后续再进行展开。

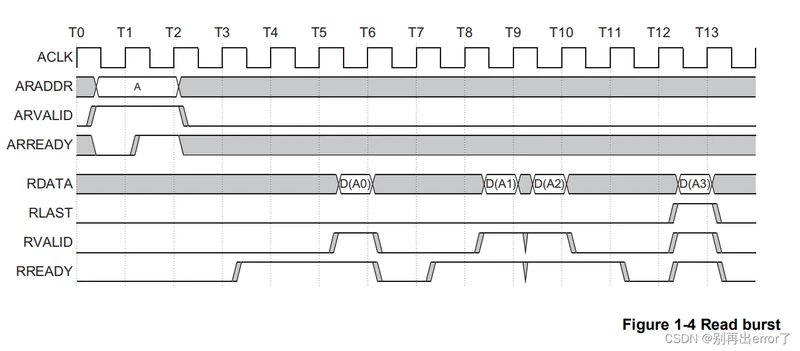

先看读写猝发的时序图:

读猝发的数据传输时序图如图所示,发送地址ARADDR时,ARVALID信号被拉高,等待ARREADY信号拉高完成握手,从而完成一个地址的传输;读数据类似,读数据传输时拉高RVALID信号,与RREADY握手后完成数据传输。而当完成一个burst的最后一笔数据包传输后,RLAST拉高,表示已经结束了最后一个包的传输。

这里在第一次看时有几个疑问;

1.master驱动读地址后数据传输发生,具体延迟多久发生的?

答:读数据操作发送在slave接收读地址之后,具体时间由slave控制

2.读操作中数据流向是slave --> master,所以在数据有效时slave会拉高valid信号,ready信号由master控制?是否会存在在读到有效数据时ready为低的情况?

答:是的,若ready为低,data会持续直到完成传输;

3.每个数据之间为什么会存在无效的间隔?

答:由slave内部控制的,可以设置burst传输各个数据包之间存在delay。

写猝发类似,从图上看,master把地址和控制信息发送在写地址通道上。之后,master往写数据通道上发送数据。当master发送最后一个数据时,WLAST信号会变高电平(和读一致)。如果slave接受了所有的数据,它将驱动一个写响应信号返回master,以表示这个写操作结束。(这里需要注意的是,写操作中写数据和写地址没有严格的先后关系,可以先发送数据,再发送地址,原因是因为写数据、写地址通道中有寄存器可以进行缓存,而地址通道寄存器比数据通道更多时,写数据可以在地址到达之前达到)

1.3传输顺序

可通过对操作进行一个ID标记,同一个ID按指定顺序(即发送前后顺序)进行操作,不同ID可以不按顺序进行,这使得AXI支持乱序传输,后进行的传输操作可能比先进行的操作要快。一个读或写猝发的各个ID(即地址、数据的ID)是一致的。

二、各个通道中的信号描述

2.1全局信号

全局时钟ACLK(上升沿采样),复位ARESRTn(低电平有效)。

2.2写地址通道信号

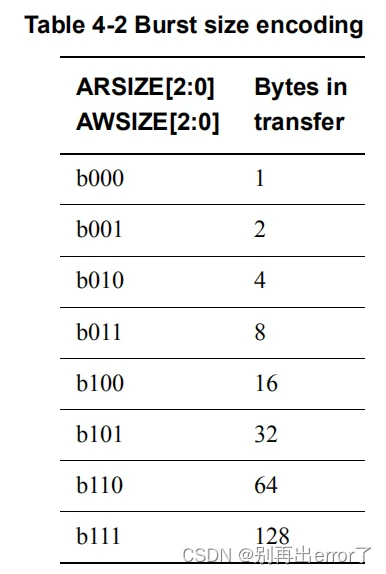

地址通道主要包含地址及控制信号,重点关注标出的几个信号:AWID为写地址ID,可通过ID控制顺序;AWADDR为第一个数据包的初始地址;AWLEN为一个burst的长度,即有多少个数据包,其值为1-16(不能超出边界);AWSIZE为一个猝发中单个数据包的传输位宽,3bits的值分别对应1,2,4,8,16,32,64,128字节;AWBURSR为burst的类型,会决定猝发方式,从而影响各个数据的地址计算;AWVALID和AWREADY为该通道的握手信号。

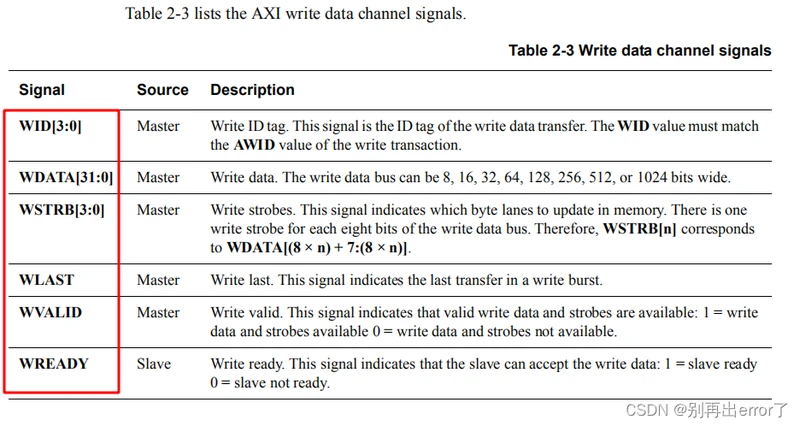

2.3写数据通道信号

这几个信号都很重要,WID不再重复,WDATA是写数据;WSRTB是字节开关,1bit对应1字节数据,即1111对应字节通道开4字节,0011对应开较低2字节;WLAST表示burst的最后一个数据完成传输,和WVALID和WREADY握手信号去之前类似。

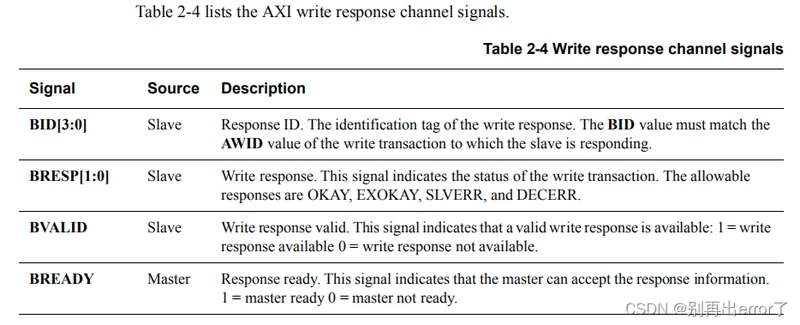

2.4写响应通道信号

BRESP为2bit数据,表明写操作的4种状态。其余信号和前文类似。

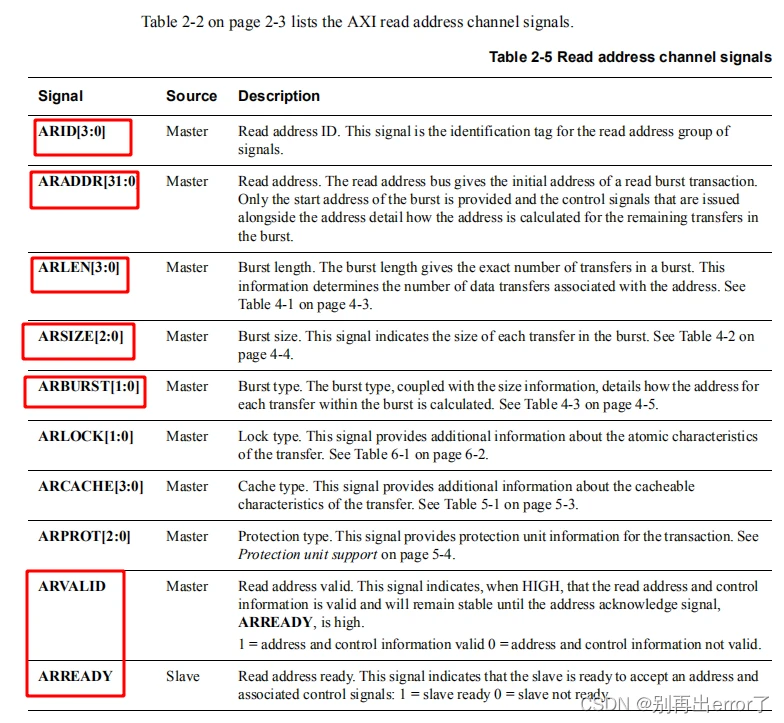

2.5读地址通道信号

与写地址通道类似,不再重复。

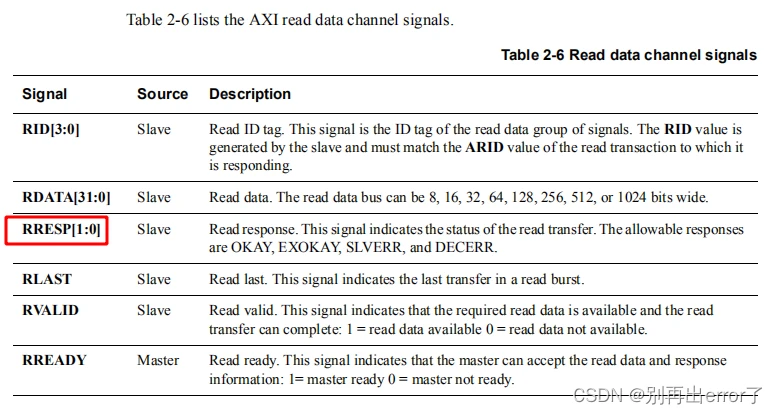

2.6读数据通道

RRESP是读响应信号,对应写响应通道的信号,读操作时响应随数据通道一同进行传输;其余信号类似。

关于在读数据没有字节开关strobe信号的问题,这里我的理解是:在写操作时,数据总线会传输完整的数据包,但在slave接收端会根据strobe确定有效的字节位,并写入对应的地址,所以需要通过strob告诉slave哪些字节数据是有效的;但在读操作时,对对应地址进行读数据,通过slave传到master的数据都是有效的,在窄带传输、非对齐等情景下只需要根据地址进行读操作即可,不需要字节开关来控制有效,因为读出的单一地址上的一字节数据是肯定有效的。

三、通道握手

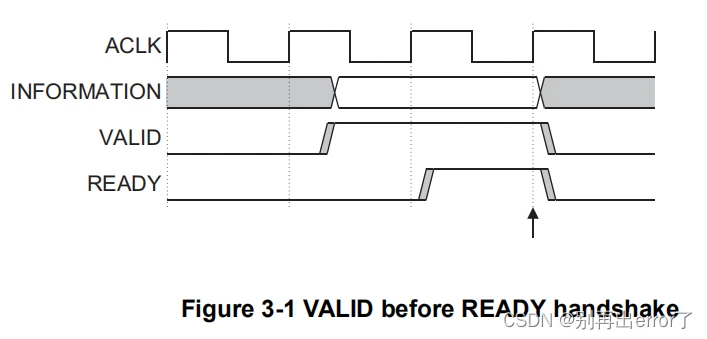

3.1单一信息传输时的握手过程

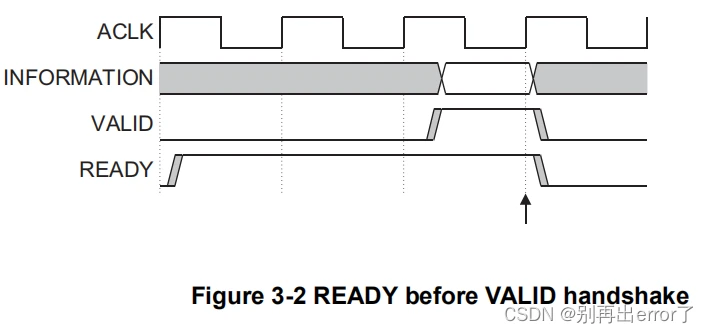

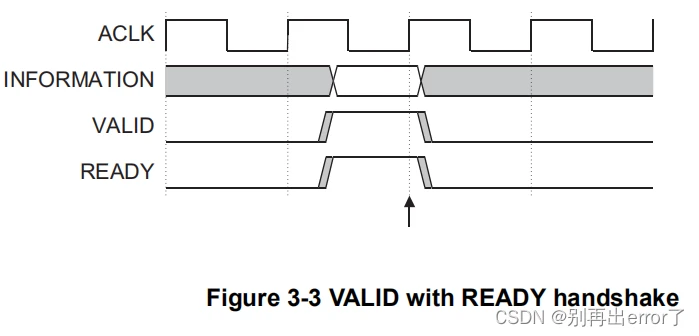

单个信号的握手比较好理解,发送方在地址或是数据有效时拉高valid信号,接收方拉高ready,两者同为高时完成一次传输。若未握手成功,数据和valid信号会一直保持,直到完成一次传输。ready拉高可以在valid之前,也可以在valid之后,或同时拉高。

3.2不同通道之间的信号握手关系

在传输操作中,valid信号不能依赖于其他部件的ready信号,否则容易出现锁死情况;而ready信号可以依赖于valid拉高,在valid置起之后再置起。(ready默认值保持高电平也可行,握手更快,更高效)

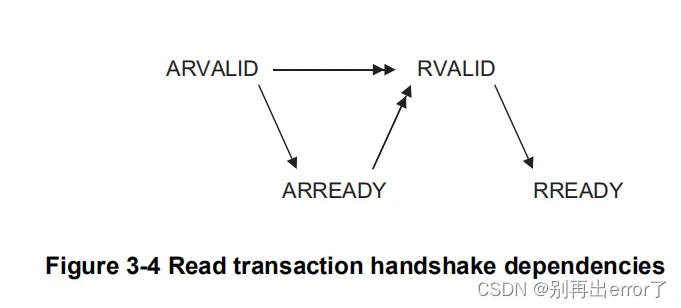

如图所示是读操作时的握手信号依赖关系,单箭头表示没有严格的前后关系,双箭头是有严格的前后关系。 即ARVALID和ARREADY没有严格的前后关系,读地址的握手必须在读数据之前,这是因为没有地址是无法得到读数据的值的。

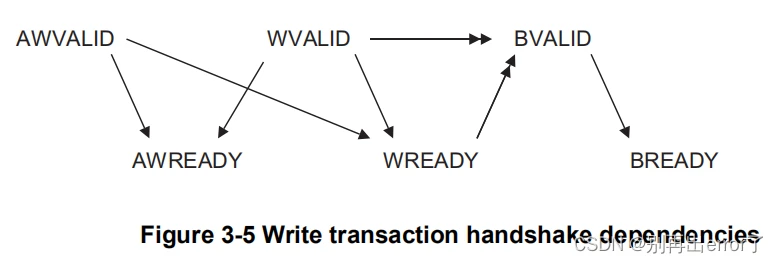

如图所示是写操作时的握手信号依赖关系,除了写响应信号的握手信号需要在最后,写地址和写数据握手信号没有严格的先后关系,即数据可以比地址先发送,这是因为通道中的寄存器可以进行缓存,等待地址达到之后再写入数据。

需要注意的是,写操作中slave中的AWREADY不必等待WVALID置起后再置起,不然可能造成锁死。

四、寻址项

AXI协议的猝发传输是如何确定地址?在一次猝发过程中,master只会通过地址传输通道发送一个基地址,而slave在接收到之后,会更具其他的控制信息进行地址的计算,以存放后续发送的其他数据。

在一次猝发传输中,数据总量不能超过4KB的边界,避免出现slave在地址增加计算时出现超出边界的情况。在这里,4KB指的是有效的数据传输总量。

猝发传输的数据数量由AWLEN或ARLEN来控制,每个猝发有1-16个数据传输。len位宽为4。而对于卷绕式传输长度必须是2,4,8,16。组件不能提前终止一个burst来减少传输的数量;在一个写猝发中,master可以通过字节开关全关来关闭后续的数据传输,但它必须完成当前的写数据传输。一次读猝发中master可以选择丢弃后续的数据包(可能造成数据丢失,例如在fifo中)。

猝发传输的数据包大小有ARSIZE或AWSIZE决定。

AXI协议由传输的地址来决定对每个传输使用哪个数据总线的字节通道(设置strobe)。对于传输的大小窄于数据总线的自增式或者卷绕式猝发,对猝发的每个数据包,数据在不同的字节通道上传输。一个固定地址的猝发,每个传输使用相同的字节通道。任何传输的大小一定不能超过数据总线的宽度(总线宽度由数据通道信号WDATA或RDATA控制)。

猝发类型有三种,分别是固定式,自增式,卷绕式。固定式猝发地址不变,会重复访问相同的区域,例如写入或读取外部fifo时;自增式猝发,猝发的每个传输的地址是在之前的传输地址基础上的增加。增加值依赖于传输数据的大小。例如,猝发式传输每个4字节大小数据的地址是在之前基础上加4,常用在一般的缓存设备中;

卷绕式猝发和自增式猝发类似,因为猝发的每个传输的地址都是在之前地址上的增加。然而,在卷绕式的猝发里,当到达了卷绕边界时地址会卷绕到一个较低的地址,常用在高速缓存中。应用卷绕式有两个限制:开始的地址必须和传输的大小对齐;猝发的长度必须为2,4,8或者16。

通过上述的控制信息,可以对猝发中的各个数据的地址进行计算,以及选择字节通道的开关,具体的计算公式略。

五、数据总线

AXI协议有2个独立的数据总线(读和写),有各自的握手信号。每一笔传输的位宽可以和总线宽度一致也可以小于总线宽度,小于总线宽度的情况被称作窄带传输。

5.1字节开关WSTRB

每一个字节开关信号对应于写数据总线上一个字节。当WSTRB为高时,字节开关指示数据总线上对应的字节部分包含内存中要更新的有效信息,即对应的数据字节有效。数据总线上每一个8比特都有一个字节开关,所以WSTRB[n]对应WDATA[(8*N)+7: 8*N)]。

5.2窄带传输

当master产生的数据传输宽度比数据总线宽度窄时,由地址和控制信息决定了传输使用哪个字节位。在递增和环回猝发传输时,每一个数据包都由不同的字节定位传输数据。在固定式猝发传输时,地址保持不变,使用的字节定位也可以保持不变。

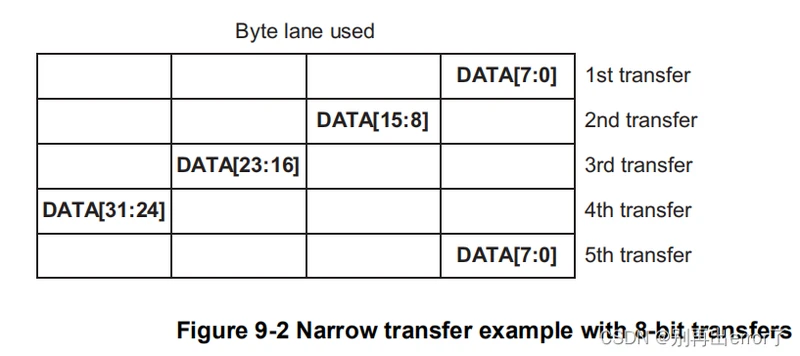

例1 :1个burst有5个传输(即len=5),起始地址为0,单个传输为8bits(size=8),传输总线是32bits,传输宽度小于总线宽度。

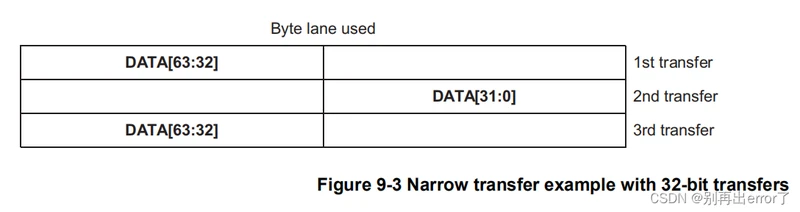

例2:1个burst有3个传输,起始地址是4,单个传输为32bits,总线宽度为64bits。

六、非对齐传输

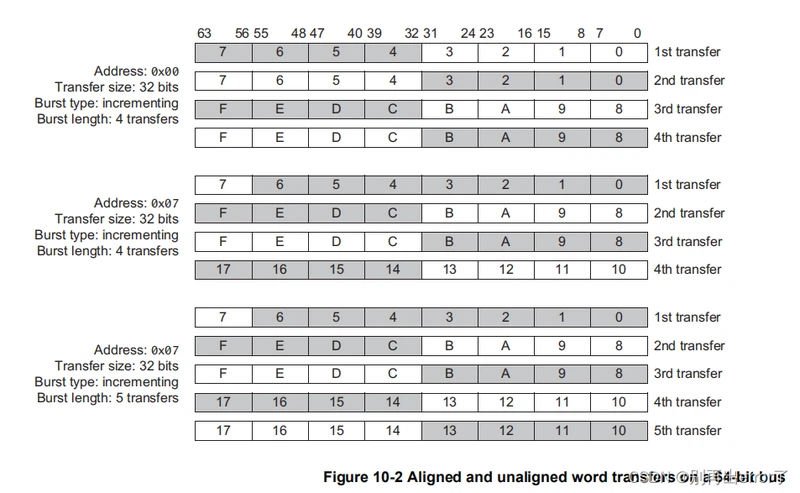

猝发传输数据大小有时是大于一个字节的,可能需要存取的前几个字节不会和数据地址边缘对齐。例如,32位(4个字节)的数据包开始于0x1002的地址,并没有和32位的地址边缘对齐(0x1000或0x1004等),这种情况就是非对齐传输。

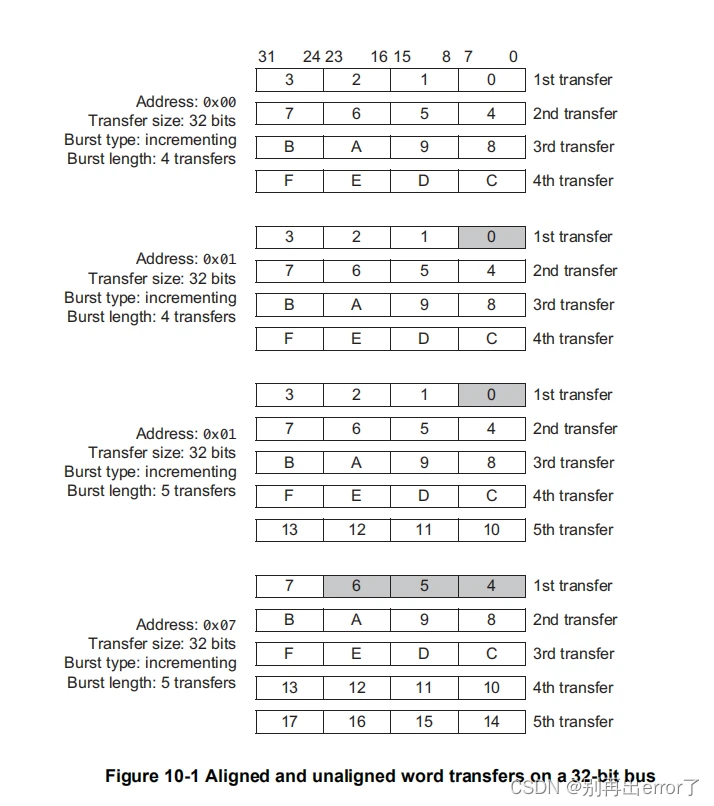

传输示例1:总线宽度为32bits,数据位宽为32,图中第1个是对齐传输的场景,后三个是非对齐传输的例子。非对齐传输的例子中,第一个传输数据的地址由于起始地址没有对齐,会导致有的地址是没有数据存取的,例如起始地址为1,地址0没有地址存取,而此时由于有效地址为并没有4字节,无法存取4字节的数据,则数据开关strobe也需要进行相匹配的数据选通,对数据进行存取。

传输示例2:总线宽度为64,数据位宽为32。第1个是对齐传输的,后2个为非对齐的传输。

七、其他

其余还有原子访问、排序、低功耗等内容,由于暂时未接触,在这里不做阐述。