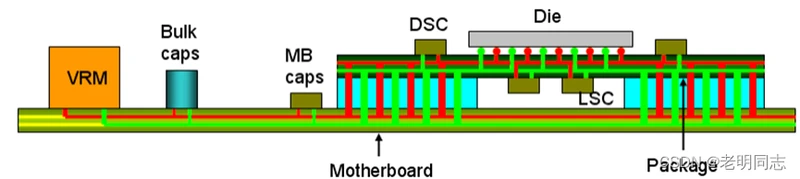

PDN是Power Distribution Network的缩写,即电源分配网络,也可以称作Power Delivery Network,即功率传输网络。其组成包含了从电源芯片到用电芯片之间的整个互连通路的所有元件和物理结构。

功率传输描述的是电功率通过PDN输送到芯片内晶体管的过程。功率是半导体器件的“粮食”。如果无法为半导体芯片提供及时的、连续的功率传送,半导体电路就会出现可靠性问题。所以可靠的功率传输是电源分配网络的基本功能。由于PDN网络并不是理想的导体,各个组成部分都存在着寄生电感、电阻特性,因此在功率传输的过程中会产生电源电压波动、功率损耗和功率传输延时。需要我们通过PCB板、封装甚至DIE上进行滤波设计来满足功率的可靠传输。

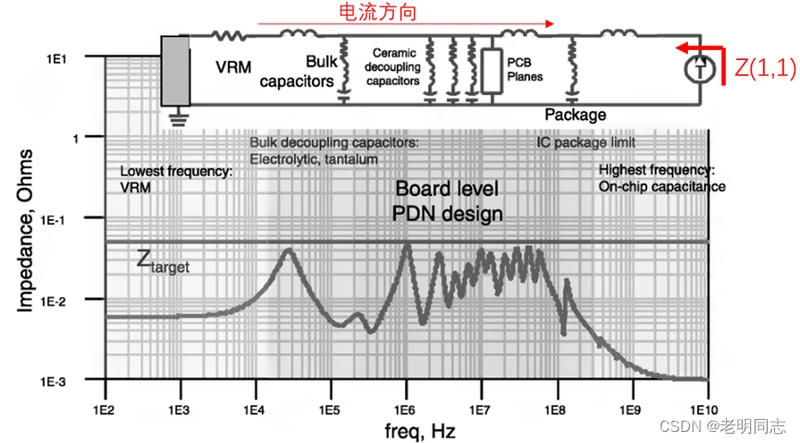

首先我们需要了解,芯片需要外部提供高频电流来满足IO翻转、指令的传输需求,而VRM能够提供的是DC到几十KHz的低频电流。

如果直接将VRM的电源供给芯片显然不能满足要求。由VRM到芯片的供电路径上不可避免的会存在过孔、平面、封装管脚以及封装内部的布线和平面等物理结构,这些结构都或多或少的表现为感性和阻性,高频电流流过会产生电源跌落。

从另一方面,电感的高频阻抗较高,对芯片需求的高频电流来说会带来功率传输的延时。为解决电感给供电系统带来的问题就需要用到各种频带的电容。VRM在非常低的频率范围内起作用,一般为DC~几十KHz;Bulk电容在几十~几百KHz起作用,一般为电解电容或者钽电容;陶瓷电容的作用频率一般为几M到几十MHz范围内;更高频率的就是电源平面的电容一般在几百MHz。此外一些高端芯片在封装内部会有封装电容、芯片的die上也会有on die decap,由于package decap和on die decap拥有很小的电感,这样就更好为芯片提供高频供电。

PDN的阻抗

PDN设计的目的就是为了保障芯片的电源供应稳定可靠,主要包含两部分内容:

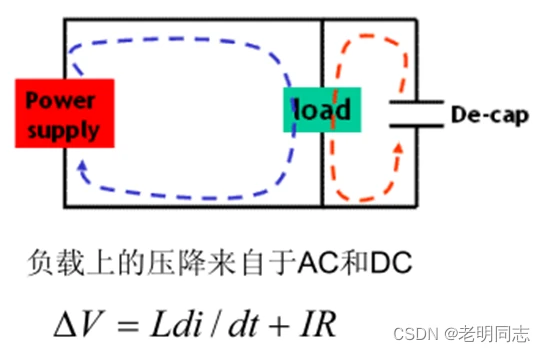

(1)电流从VRM输出到芯片端由于直流电阻的存在会产生一个IR drop;

(2)VRM和芯片的高频电流需求使得电源产生电压噪声。

IR Drop与PDN的直流电阻有关,电源噪声和PDN的交流阻抗相关。电流一定的情况下电阻和阻抗越小IR Drop和电源噪声越小。

IR drop比较好理解,这里不再过多阐述。

而PDN的阻抗我们通常用负载端的自阻抗来衡量。所谓自阻抗就是从芯片负载向VRM看去的阻抗,我们可以想象一下,芯片负载是电流的需求方,它要将电流从VRM拉到自己这里,那么自阻抗越小就越省力,产生的噪声也就越小。

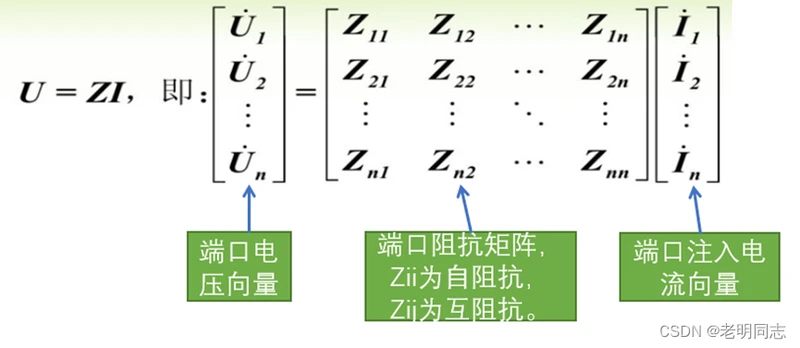

为了帮助理解,这里简要解释一下Z参数的概念。对于一个多端口网络,分别用Ui、Ii表示每个端口的电压和电流,Z表示阻抗。列出矩阵方程如下:

自阻抗的定义 : Zii=Ui/Ii,Ij =0,j ≠i 。

自阻抗的物理意义,在端口i注入电流,其余端口都没有注入电流时在端口 i产生的电压 。PI仿真中主要是看PDN自阻抗,自阻抗越小PDN性能越好。

互阻抗的定义 : Zji=Uj/Ii ,Ij =0,j ≠i

互阻抗的物理意义,在端口i注入电流,其余端口都没有注入电流时在端口 j产生的电压 。互阻抗描述了两个端口间的相互干扰,互阻抗越小两个端口之间的相互干扰越小。当一个PDN用存在多个用电芯片时,为了避免负载之间的相互干扰就需要对其互阻抗进行分析。

这一节主要介绍了PDN的组成以及PDN的阻抗定义,下一节详细介绍PDN的各个组成部分。