1.IO划分

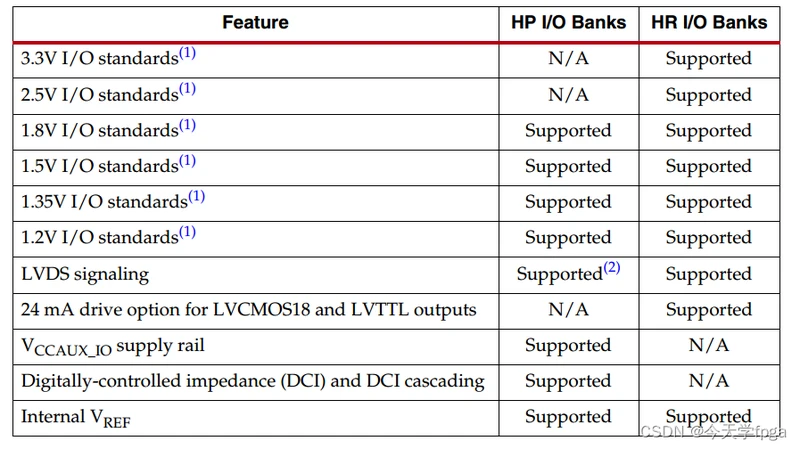

xilinx 7系列FPGA的I/O接口以及I/O逻辑的总称为SelectIO。 I/O bank分为高性能(HP)banks和宽范围(HR)banks。HP I/O banks可以实现高性能存储器接口或者芯片间高速接口,支持电压最大1.8V,HR I/O banks支持更宽范围的I/O电平标准,最大支持3.3V。这两种I/O banks支持的I/O特性如图所示:

每个IO BANK包含50个IOB,其中两个只能做单端IO,其余48个可以配置成24对差分IO。

2.IO资源介绍

IO资源包含两部分,IOB和IO逻辑部分

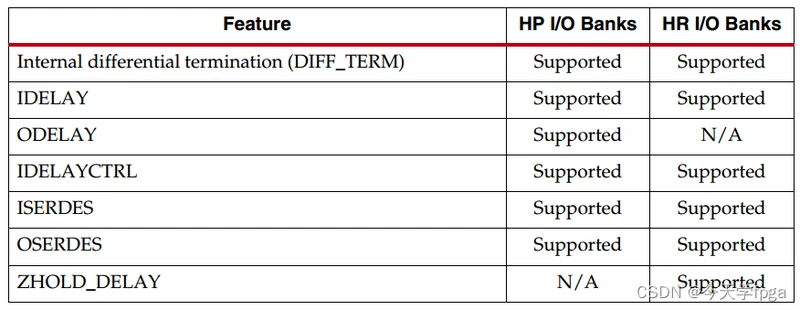

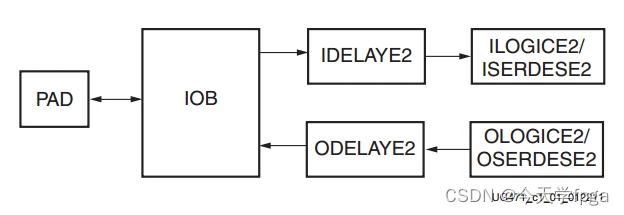

HP BANK的IO资源:

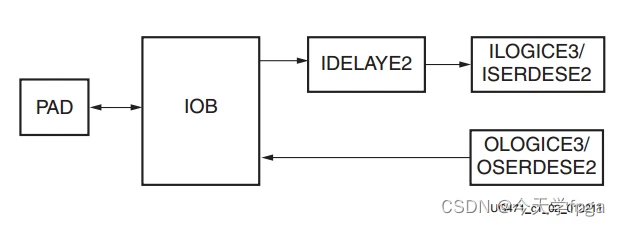

HR BANK的IO资源:

HP bank 具有单独的 IDELAY 和 ODELAY 块,但是HR bank没有ODELAY 块,其余大致相同。

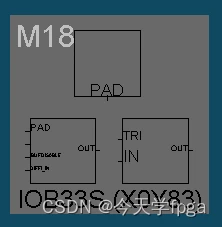

IOB

IOB就是IO buffer的意思,每一个IOB包含两个IO口,一个PAD。两个IO口分为输入input,输出output。PAD就是与外部连接的焊盘。7系列中,50个IOB组成一个IO bank。

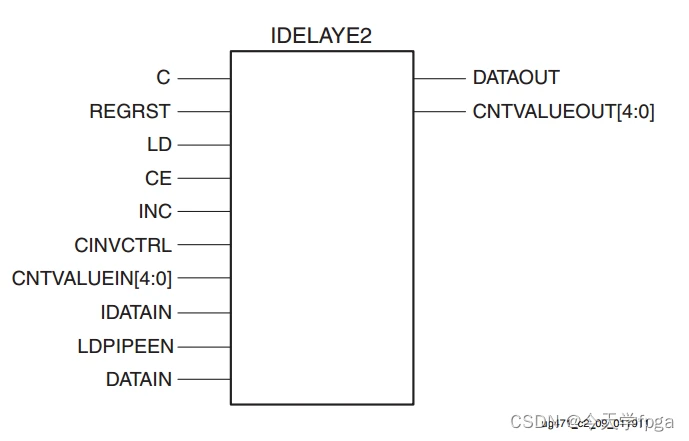

I\ODELAY

IDELAY被称为信号延迟模块,它的作用就是把信号延迟一段时间。可以用在:1、信号对齐;2、高速信号处理时,避免在信号转换时采集,将数据进行延迟。在7系列FPGA中,它被称为IDELAYE2。IDELAYE2可以将信号延迟0~31节,在这区间任意可调,并且每节的延迟精度约为78ps(1/(32×2×FREF),FREF为IDELAYCTRL的参考时钟)。

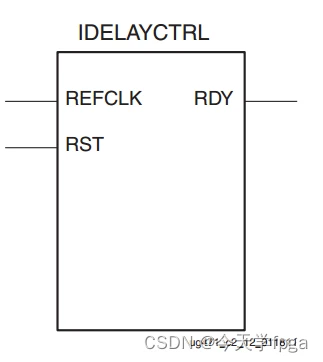

使用IDELAY模块必须用到IDELAYCTRL,IDELAYCTRL为IDELAY提供延迟精度,起辅助作用,他的参考时钟一般为200MHZ。

ODELAY作用相似,只不过是针对输出。

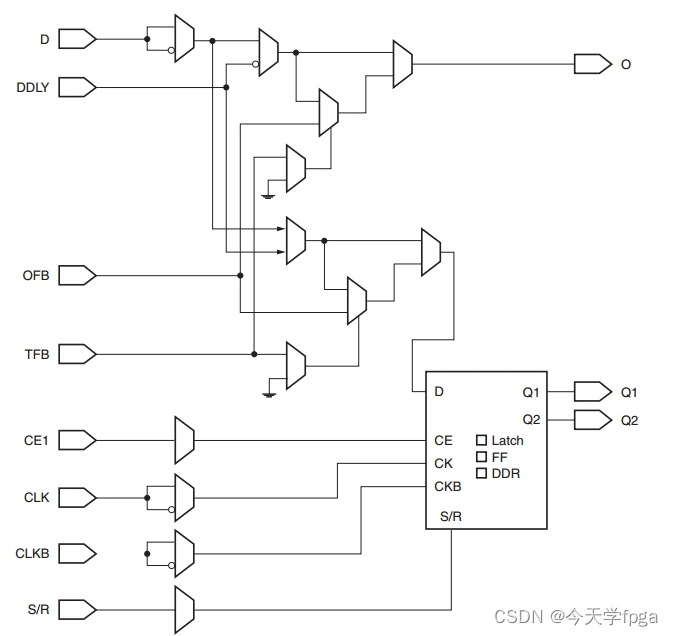

I\OLOGIC

ILOGIC是由许多的数据选择器和一个IDDR(input Double data rate)触发器构成。该触发器既可以双沿捕获输入数据也可以拆分成普通单沿触发器。

ILOGIC根据不同的用法配置成:

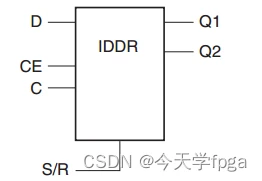

1.IDDR

将1 bit的双沿采样输入转换为2bit的单沿采样输出

然后,IDDR可以配置成三种模式

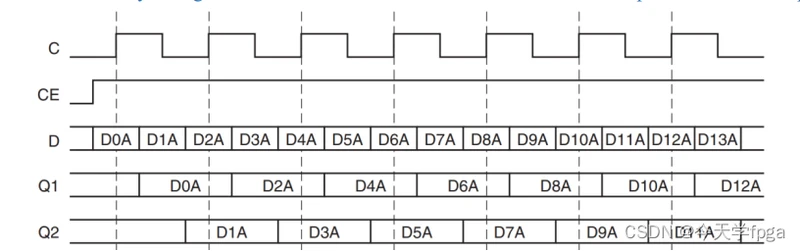

OPPOSITE_EDGE:在时钟的上升沿输出的 Q1,时钟的下降沿输出 Q2

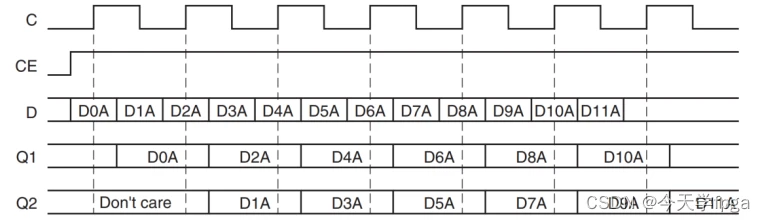

SAME_EDGE:在时钟的上升沿输出 Q1 和 Q2,但 Q1 和 Q2 不在同一个 cycle 输出

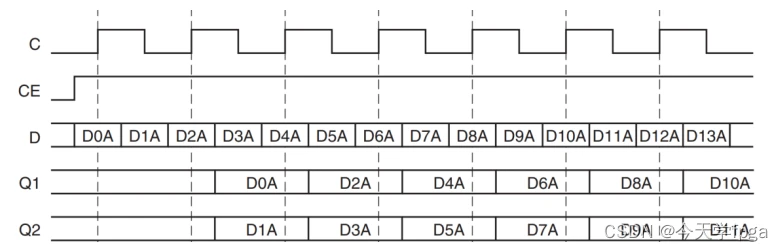

SAME_EDGE_PIPELINED:在时钟的上升沿输出 Q1 和 Q2, Q1 和 Q2 虽然在同一个 cycle 输出,但整体延时了一个时钟周期。一般使用这个模式

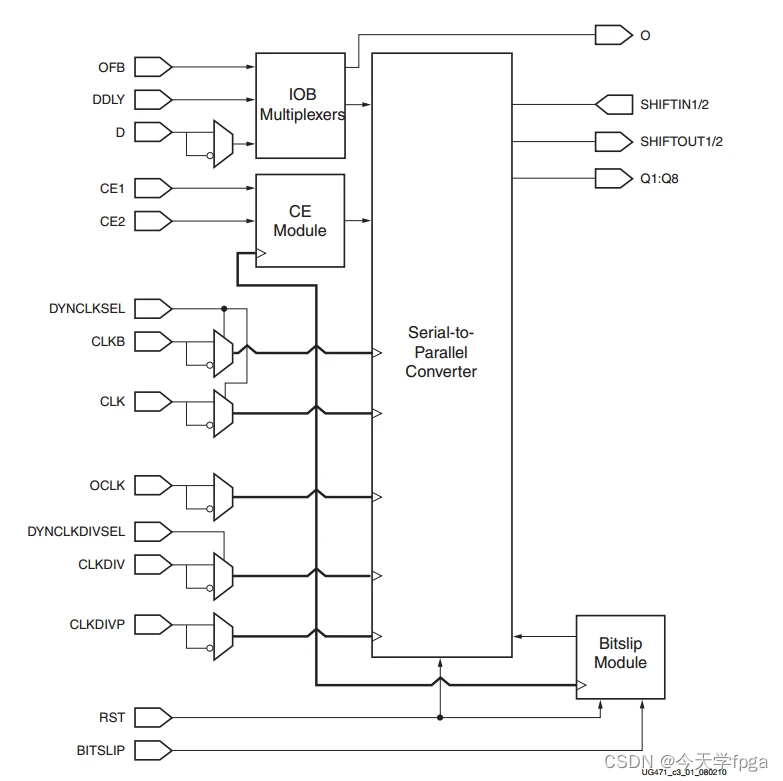

- ISERDESE2

ISERDESE2可以理解为解串器,实现高速源同步输入数据的串并转换。如图为示意图,按照功能分成5个部分:

a, 外部串行数据输入端

该部分接收外部输入的高速源同步数据,数据可以为SDR或者DDR。在SDR模式时,数据转换的位宽可以为2、3、4、5、6、7、8bit。在DDR模式时,数据转换位宽为4、6、8bit,当然如果是2个ISERDESE2级联使用,DDR模式可以支持10、14bit。

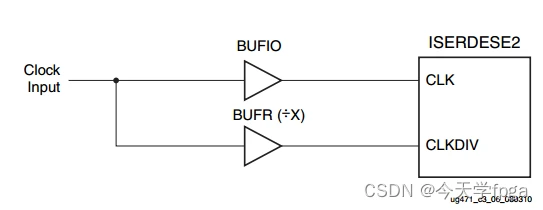

b, 时钟接口

该部分提供ISERDESE2工作的高速源同步串行时钟、并行数据获取时钟以及控制时钟。如图2所示为源同步时钟接入ISERDESE2的用法。SDR模式只输入CLK,DDR模式需要输入分频时钟

c, 并行数据输出端

该接口就不用多说了,就是最终咱们需要的并行数据。SDR模式下为2、3、4、5、6、7、8bit,DDR模式下为4、6、8、10、14bit。

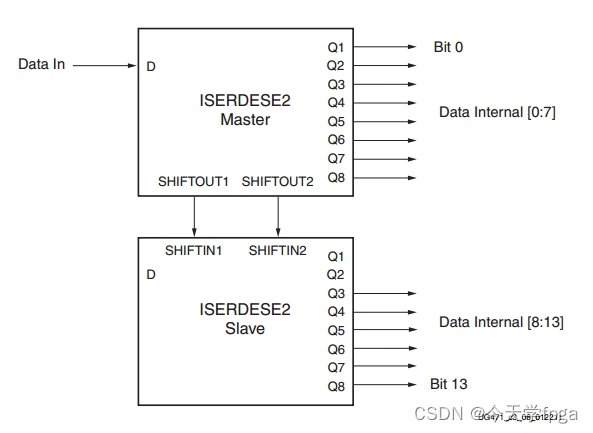

d, 级联接口

该接口是实现DDR模式下10bit、14bit位宽的关键接口,通过该接口与另外一ISERDESE2级联,两者共同完成10bit、14bit数据的串并转换。如图3即为2个ISERDESE2的级联用。

e, 数据对齐模块

该模块又称作Bitslip模块,用来实现并行数据的边界对齐。比如咱们外界串行输入的8bit的数据,经过串并转换后,能获取8bit的并行数据,但这并行数据可能存在前后8bit数据之间的错位,这是串并转换无法识别的,因此Bitslip就专门用来找到用户需要的并行数据边界。

OLOGIC根据不同的用法配置成:

1.ODDR

将2 bit的双沿采样输入转换为1bit的单沿采样输出,其余同IDDR

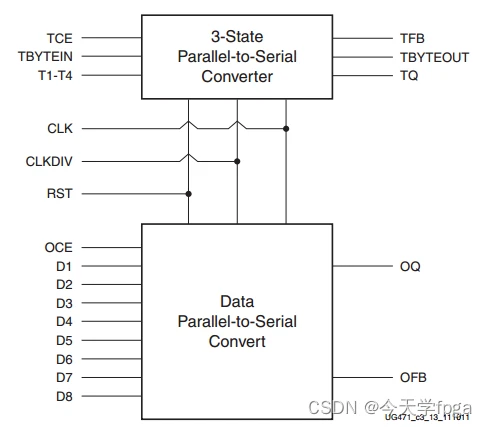

2.OSERDESE2

OSERDESE2可以理解为串行器,实现高速源同步输入数据的并串转换。如图为示意图,多了一个三态控制模块(负责数据的选择性输出),少了Bitslip模块:

3.IO资源使用

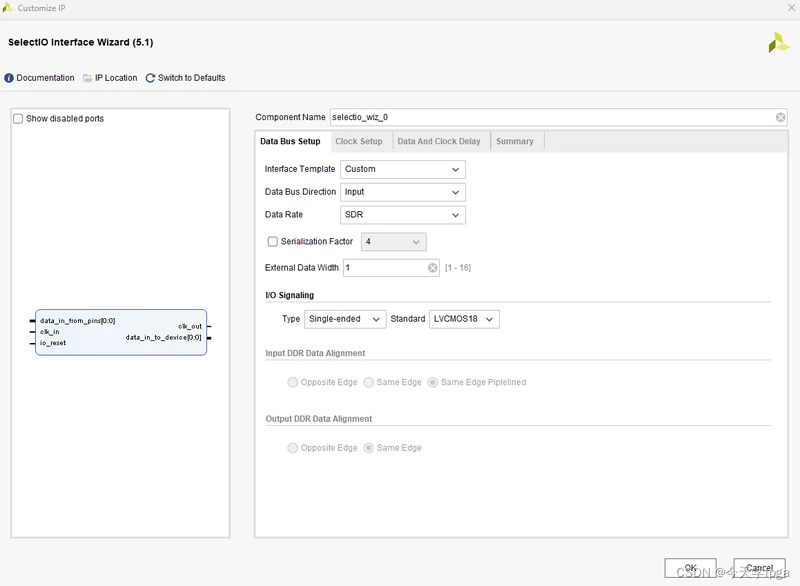

1.SelectIO IP核

可以调用SelectIO IP核配置所用的IO资源

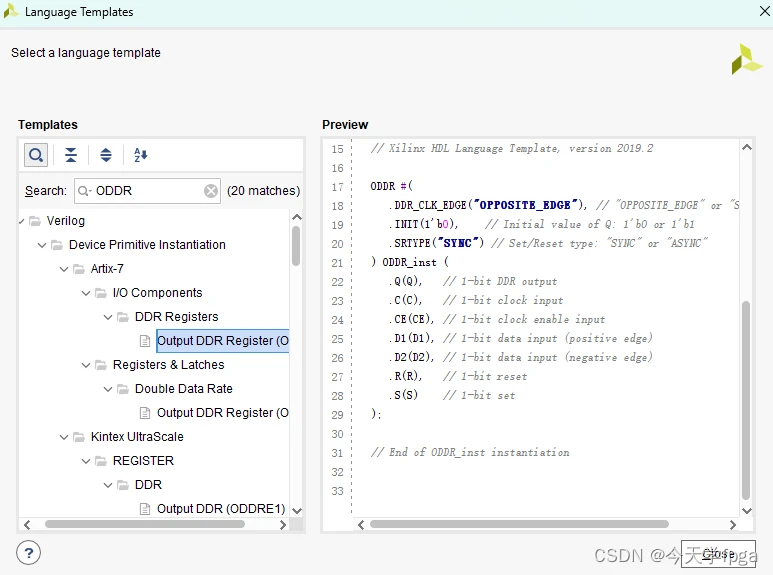

2. 原语

可以使用XILINX提供的原语使用对应的IO资源,VIVADO提供有原语模板,位置:Tools --Language Templates。但是需要注意的是需要使用对应芯片系列的原语,因为不同系列芯片上的硬核资源有所不同。

参考:

https://docs.xilinx.com/v/u/en-US/ug471_7Series_SelectIO

https://zhuanlan.zhihu.com/p/117314318