一、闩锁效应原理

定义:

闩锁效应是cmos工艺所特有的寄生效应。闩锁效应是由nmos有源区、p衬底、n阱、pmos的有源区构成的n-p-n-p结构,寄生成的两个相关的三极管产生的,严重会导致电路的失效,甚至烧毁芯片。

闩锁情况下,器件在电源和地之间形成短路,通过三极管放大电流,造成大电流,EOS(电过载)和器件损坏。是半导体失效的主要原因之一。

三极管具有放大电流作用

当加在三极管发射结的电压大于pn节的导通电压,并处于某一恰当的值时,三极管的发射结正向偏置,集电极反向偏置。这时基极电流对集电极电流起着控制作用,使三极管具有电流放大作用,其电流放大倍数β=△Ic/△Ⅰb,这时三级管处放大状态。

β实际是由三个极横截面积,三个极掺杂浓度和基极的厚度决定

二、闩锁的剖面图、原理图分析

Latch up是Pmos和Nmos之间寄生的三极管pnp和npn相互关联形成

下图以INV为例,

SCR:可控硅。

Latch up原理分析:

当有外界触发,其中一个BJT的集电极电流受外部干扰突然到一定值时,会反馈至另一个BJT(一般NPN较易触发),使Q1、Q2导通。∵Ⅰc=βⅠb,导致无限正反馈(使三极管烧毁),就算之后干扰消失,还是会有地和电源之间的漏电,即锁定状态,Latch up形成

想要Latch up发生的重要条件是β1╳B2>1

三、版图的Latch up原因分析

1.芯片一开始工作时VDD的突然变化会导致nwell和p substrate间寄生电容中产生足够的电流,当VDD变化率达到一定地步,将会引起Latch up。这种原因主要是Rnwell过大。

2. 信号变化超过VDD一GND(Vss)范围时,有大电流在芯片中产生,也会导致SCR的触发

3.ESD发生时引入少量带电载子到well或substrate中,也会引起SCR的触发

4.当很多的驱动器同时动作,负载过大使power和gnd突然变化,也可能打开SCR的一个BJT

5.有大功率器件,导致周围衬底有大电流涌动的地方,容易触发SCR

6.高压阱和低压阱(有大压差)之间容易发生SCR

7.PAD连接的器件地方容易发生SCR。在Latch up可靠性测试的时候PIN接负电位,会导致PIN连接的管子直接正偏,向周围衬底吸电流。

1.2.可总结为有高频信号的地方容易发生Latch up

3.4.5.可总结为衬底有大电流波动地方和周围容易发生Latch up

6.7.可总结为阱电位有可能接近或低于地电位的时候容易发生Latch up

①如果把n+变成nwell还是SCR结构吗?

是,n+和nwell只是浓度不同

②相同条件下大面积Nwell容易触发Latch up还是小面积容易触发?

当Nwell替代N+成为集电极的时候,面积更大,阱深更深,对应的基极和截面积更大,同时吸收的衬底电流更大,整体寄生三极管周围环境更加复杂,距离Psub衬底接触更远,导致Rsub更大。

即,C面积变大,收集电子变多,∴大面积更易触发

只要是接地的NWELL,不管里面是pmos还是nmos,都与接电的NWELL容易发生Latch up

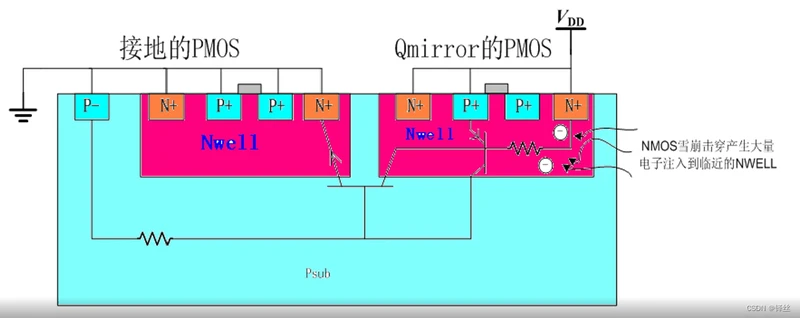

下图为NWELL接地或低电位的原理图,可看出与(P/Nmos间)Latch up相同

四、版图的Latch up可靠性分析

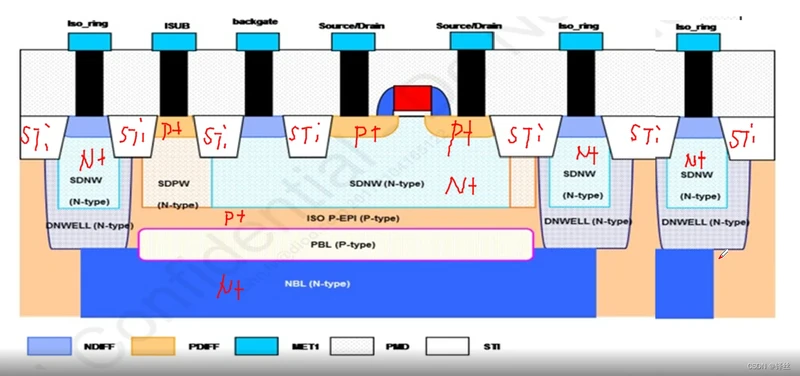

1.工艺上采取衬底隔离的方式

通过衬底隔离,把衬底电流的影响隔离在MOS管外面,或者说不让对衬底有影响的大电流经过衬底Psub

深Nwell一定要接高电位

与layout相关的例子,如下:

用DNwell的情况(一般不用,∵面积太大)

1.当电路有负压时,一定要有深Nwell,否则区别不开

2.作隔离噪声,

3.Latch up

2.在pmos和nmos都围P+、N+双保护环

可以部分破坏Latch up结构

双保护可以吸收衬底噪声,可以阻止载流子到达BJT的基极,减少衬底电流引起的寄生SCR结构上的电压波动(注意N环的电位)

部分时候可以降低衬底电阻,如下图N+保护环(中间红色区域)没有起到降低衬底电阻作用

从左往右数,第三个P+作用是降低衬底电阻,吸收空穴(由最右边红色区域Nwell上的p+雪崩击穿产生的空穴,穿过Nwell产生的)

第三个N+作用是提前吸收电子(由最左边红色区域Nwell上的N+雪崩击穿产生的,防止到最右边Nwell产生压降)

这两个P+,N+位置不能改变

3. 避免source和drain的正向偏压

substrate contact和well contact应尽量靠近D、S端,同时在电流大的地方多打衬底接触孔,以降低组织Rwell和Rsub的阻值,这样就可以pick up住寄生二级管两端的电位,防止寄生三极管的正向导通

4.拉开两个寄生三级管的间距

拉开间距可以增加积极厚度,使β1ⅹB2<1,拉开间距后,通路上的寄生电阻变大,导致电流变小,需要更大的衬底电流波动才会触发Latch up