一、发起沿和捕获沿

发起沿:数据发送的时钟沿叫发起沿。

捕获沿:数据接收的时钟沿叫捕获沿。

发起沿和捕获沿之间一般情况下相差一个时钟周期。

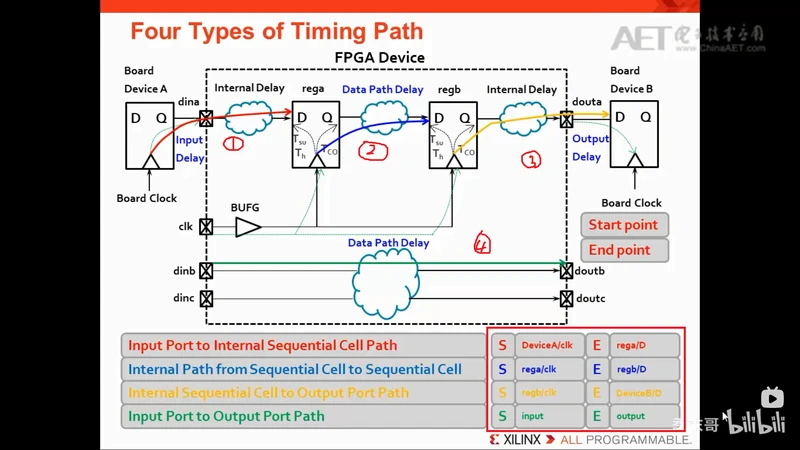

二、四种时序路径模型

1.外部输入端口到内部寄存器的路径。

2.内部寄存器之间的时序路径。

3.内部寄存器到外部端口的时序路径。

4.输入到输出的组合路径。

上述四种时序路径的起点和终点

start end point

1.Device A/clk rega/D

2.rega/clk regb/D

3.regb/clk Device B/D

4.input output

事实上前3类时序路径我们可以归结为一类:从一个寄存器的时钟端口到另一个寄存器的数据端口。只不过它们有可能在芯片内部,有可能从外部到内部。

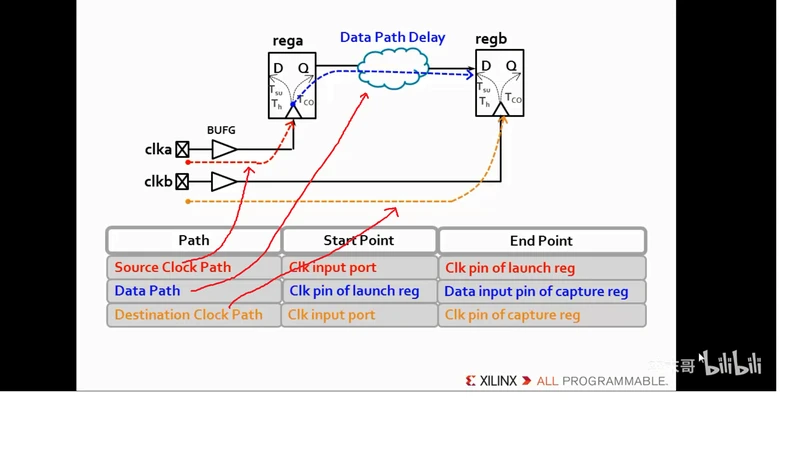

时序模型的抽象

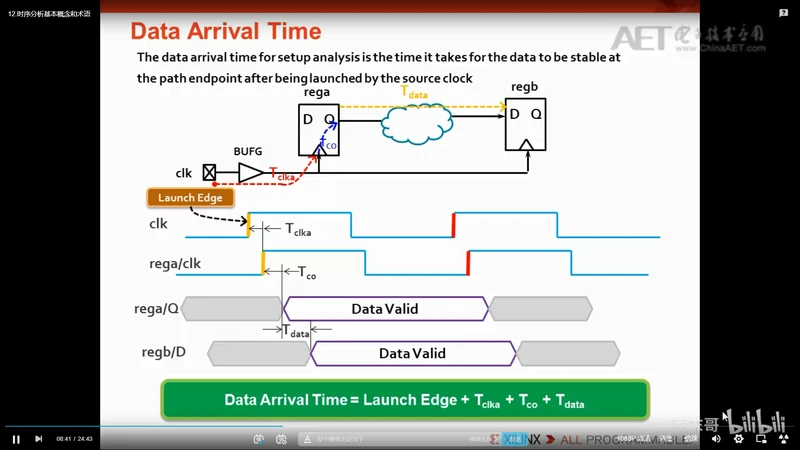

三、数据到达时间、时钟到达时间、数据需求时间

数据到达时间的概念:数据从发送沿发起之后,经过多久时间到达接收寄存器的数据端口。既然计算时间,我们需要有时间的基准点,默认将发送沿作为0时间发送点。

数据到达时间=时钟传输延时+寄存器传输延时+组合逻辑延时

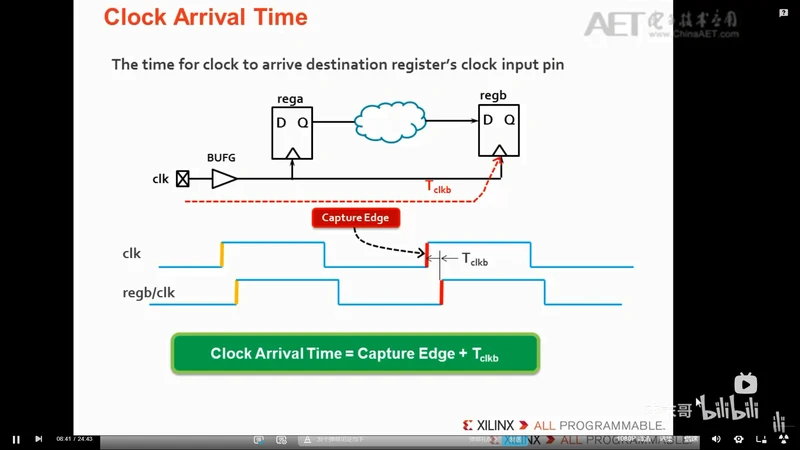

时钟到达时间指的是时钟从发起沿开始到达目的寄存器的时间,时间的基点是时钟的发起沿。

clock arrival time = capture edge + Tclkb ;而捕获沿和发起沿之间有一个时钟周期,所以时钟到达时间clock arrival time = clock period + Tclkb

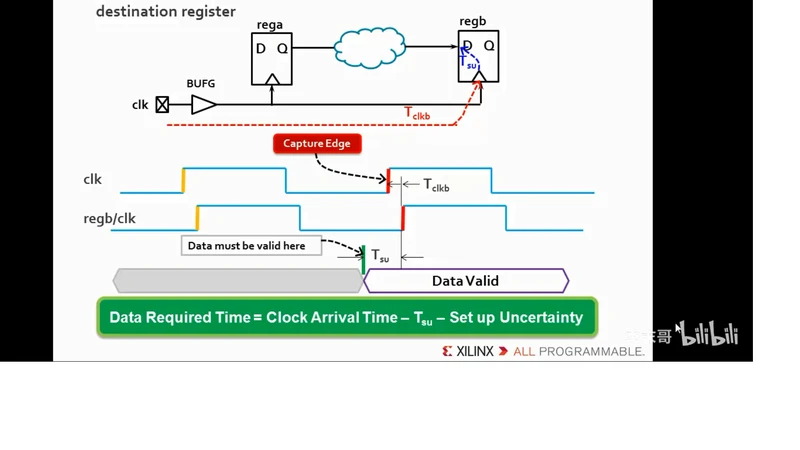

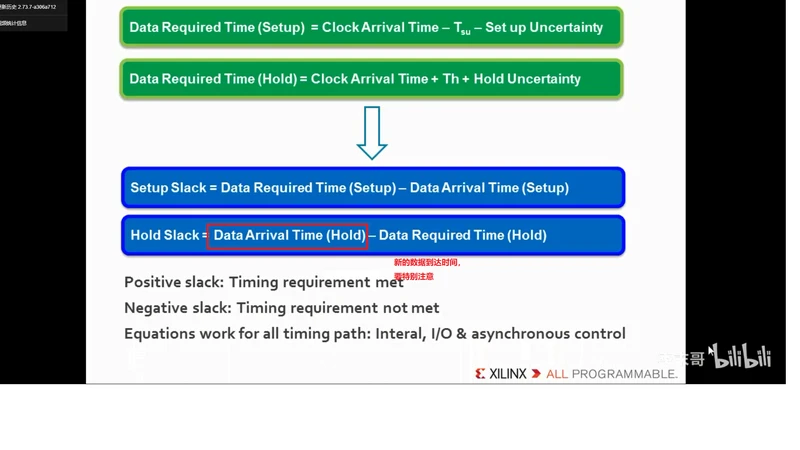

数据需求时间–建立时间

目的寄存器要正确地捕获数据,因为寄存器的建立时间要求,数据必须提前Tsu到达目的寄存器。要使目的寄存器正确地采集到数据必须在捕获沿提前Tsu到达,同时考虑到时钟抖动,所以数据需求时间为

data required time = clock arrival time - Tsu - set up uncertainty

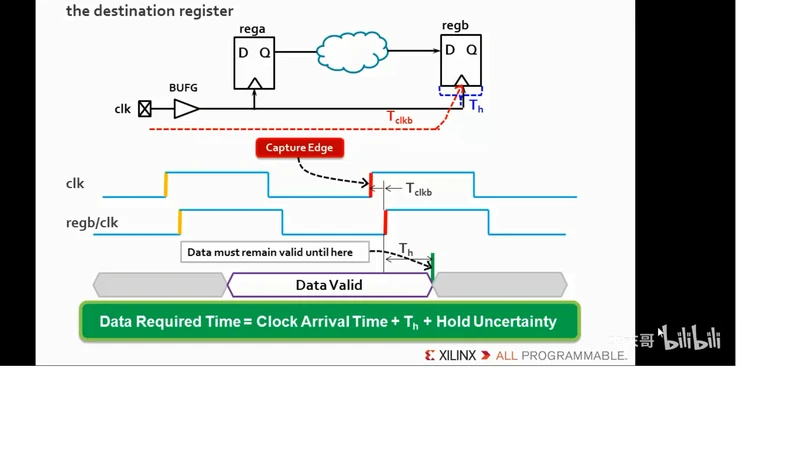

数据需求时间–保持时间

当捕获到数据之后,数据还应该稳定地存在一定时间,这个时间叫保持时间。换句话说新的数据不能提前到,否则就将现在的数据冲了。

data_require_tiem=clock arrival time + Th + Hold uncertain

同时,我们也可以知道数据的有效窗口就是Tsu+Th,它们共同构成了数据的有效窗口。

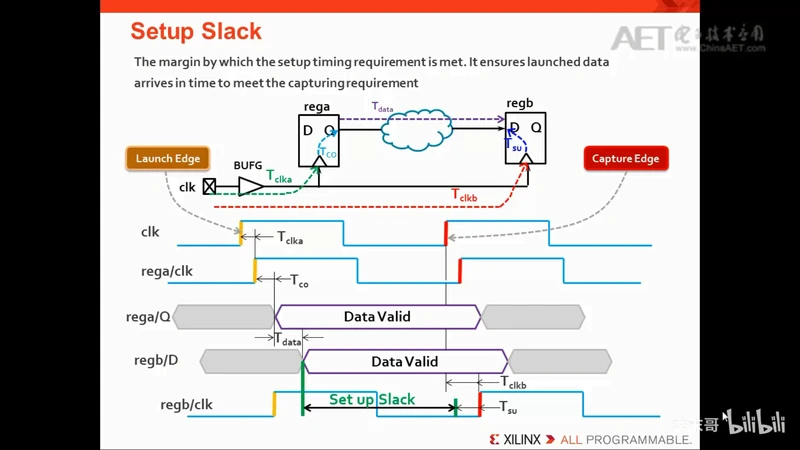

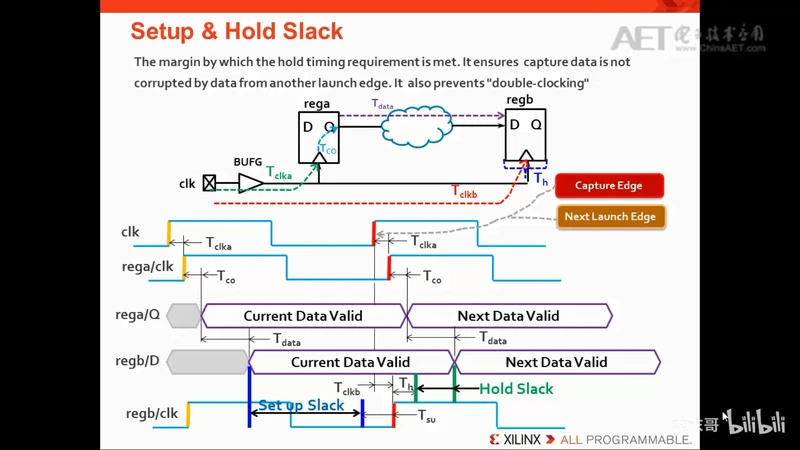

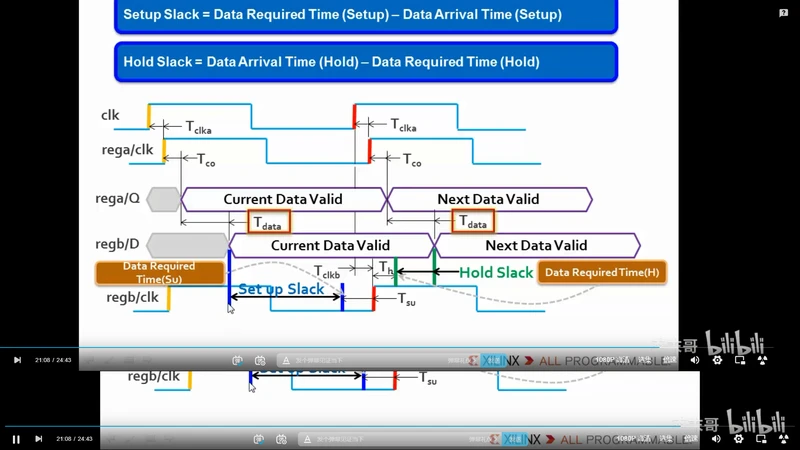

建立时间裕量

建立时间裕量=数据需要时间-数据达到时间

数据需要时间=clk_period + Tclkb - Tsu

数据到达时间=Tclka + Tco + Tdata

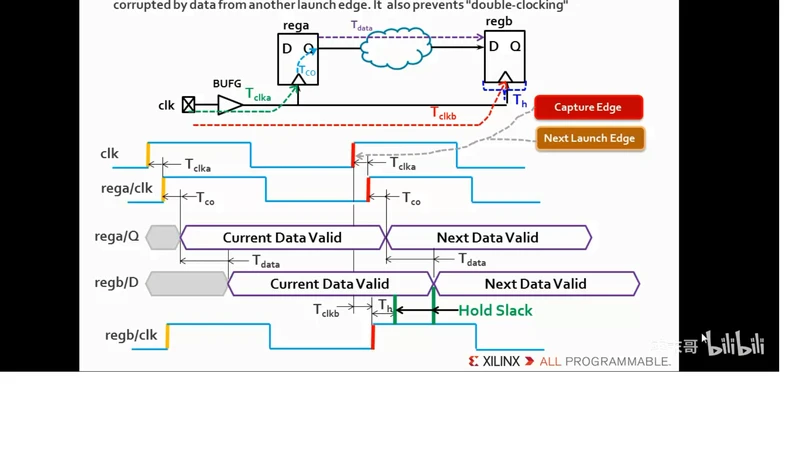

保持时间裕量

数据经过时钟延时+寄存器传输延时+组合逻辑延时到达regb的D端口,被regb采集下来,要使数据稳定,数据必须保持一定时间不变,不能被新数据的刷了。所以保持时间裕量=新数据到达时间-保持需要时间。

建立时间裕量和保持时间裕量

从上图可以看出建立时间裕量=数据需求时间-数据到达时间

保持时间裕量=新的数据到达时间-数据需求时间

此公式适用于fpga内部、IO、异步控制等。如果裕量为正,满足要求,反之不满足要求。

为什么会出现建立和保持时间的负裕量?

建立时间负裕量说明,说明数据到达时间小于数据需要时间。即就是数据到达时间太晚,无法满足建立时间。数据延时太大了。

保持时间负裕量说明数据需求时间太大了,也就是说时钟的延迟太大了。

由此可知建立时间不满足,是数据延迟太大,保持时间不满足是时钟延迟太大了。

Tdata=Tlogic+ Tnet 组合逻辑延时和走线延时,Tlogic和代码风格有关系,Tnet是延时过大与布线策略有关系,所以建立时间不满足要从代码风格和布线策略入手。