前言

之前我们也学过OTP,但是站在的维度是比较高的,不对应该是角度。我们站在使用者的角度来看的。

今天我们站在芯片设计人员的角度来看一下OTP的设计相关。

学习内容来自前辈:https://zhuanlan.zhihu.com/p/404680588

1、OTP概述

-

MTP: Multiple-Time Programmable,可以多次编程

-

FTP: Few-Time Programmable,可编程的次数有限

-

OTP: One-Time Programmable,只允许编程一次,一旦被编程,数据永久有效

OTP(one time programmable)器件,也就是一次性可编程器件,归属于非易失性存储器,相对于多次性可编程器件如MTP,Flash等,其编程过程是不可逆的,适用于程序固定不变的应用场合。

由于其成本低于多次性可编程器件,适合用在具有一定灵活性、成本不高和性能需要刷新的电子产品中,如电源管理芯片[1]。

电源管理芯片以模拟电路为主,受工艺制造等误差的影响,流片回来的芯片往往需要对作参数校准,通过在芯片中添加OTP和寄存器,调试完成后将确定的值烧写到OTP中,芯片上电后OTP的值被装载到寄存器中,模拟电路参数完成校准。

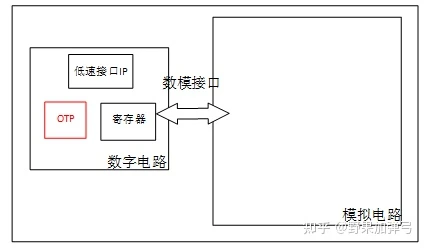

图 1是一种常见的模拟芯片电路系统框图,芯片上电后将OTP的数值装载到寄存器中完成模拟电路的参数校准,嵌入低速接口IP(常选用I2C/SPI/UART等)方便进行OTP、寄存器的读写,大大提高了调试的便捷性。

OTP通常由IP厂商提供,本文以EMEMORY提供的TSMC0.18um BCD工艺OTP为例,从一个数字设计人员的角度总结OTP读写控制需要关注的信息和注意事项。

2、OTP接口

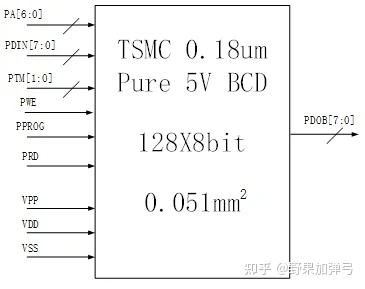

OTP的数据手册上详细记载了其容量、IP面积、工艺细节、电器特性等,这些参数通过查阅数据手册可知,此处不作过多讲解。首先需要关注的是OTP的引脚信息,如图 2所示。

-

PA:地址线

-

PDIN:写数据线

-

PDOB:OTP读数据线

-

PTM:测试模式使能,不同的工作模式数值不同

-

PWE/PPROG:OTP烧写控制引脚

-

PRD:OTP读控制引脚

-

VSS/VDD/VPP:电源相关引脚

3、OTP时序

3.1、OTP上电时序

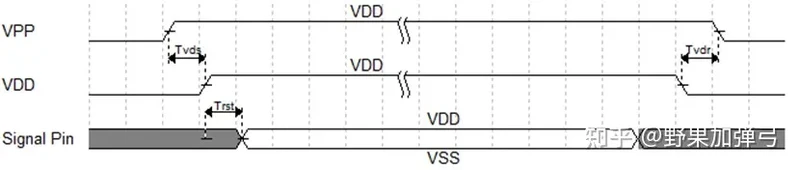

图 3是OTP的上电时序图,VSS是OTP的地,VDD电源引脚是OTP的Power supply,只要OTP工作就必须接通,VPP是OTP的高压电源引脚,一般在OTP烧写时需要灌高压,而在OTP的读时悬空或与VDD电压相同。

尽管多数OTP数据手册上Tvds和Tvdr的参数都标为0,但我们在设计控制电路时还是按照图示的上电顺序进行设计,印象中在某个项目的设计中,VDD和VPP设计为同时掉电,虽然在实际应用中二者同时掉电没有问题,但仿真时模型还是报了一个warning,所以建议还是严格按照上电时序图进行逻辑设计。

Trst(Control Signal Enable Time)是一个重要的时序参数(min=20ns),其表示当VDD信号稳定后OTP引脚信号需要等待的最少时长。

3.2、OTP控制PIN与PTM的时序

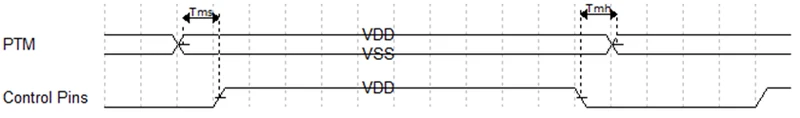

图 4中Tms和Tmh分别是指PTM Mode Setup Time和PTM Mode Hold Time,其表示Control Pins上升沿到来前PTM需要保持稳定的最短时间和Control Pins下降沿到来后PTM需要保持稳定的最短时间。

Control Pins指PRD、PPROG、PWE。值得一提的是,OTP通常都是运行在用户模式,读数据或者烧写,这两种情况下PTM的值都是2’b00,所以PTM的值一般上电后都是维持恒定不变,如果你的设计中存在PTM的值发生变化的情况,这点是要特别注意的。

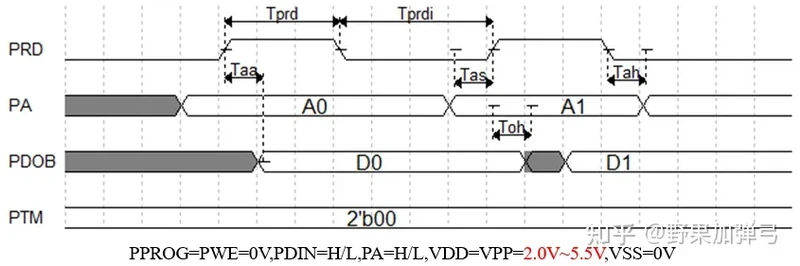

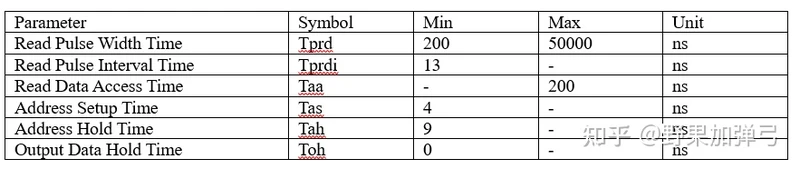

3.3、OTP用户模式读数据时序

从图 5的时序可以整理出一个OTP读数据的大概流程:

-

1、 给VPP通电,5V

-

2、 给VDD通电,5V

-

3、 准备好地址数据PA

-

4、 拉高PRD,等待PDOB数据输出

-

5、 拉低PRD

-

6、 关闭VDD

-

7、 关闭VPP

以上给出的只是一个粗糙的大概流程,具体的设计需要结合项目中的时钟来考虑,图 5中标示出来的所有时序参数在设计中都要考虑。

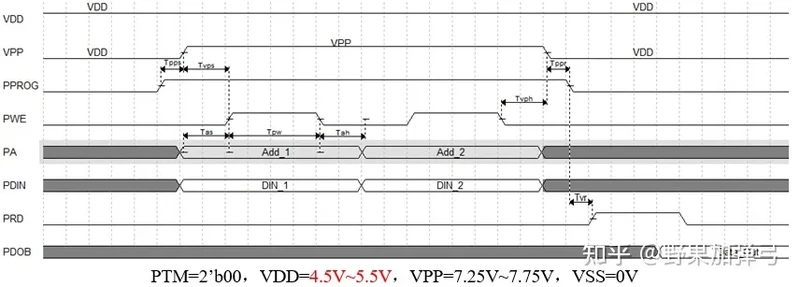

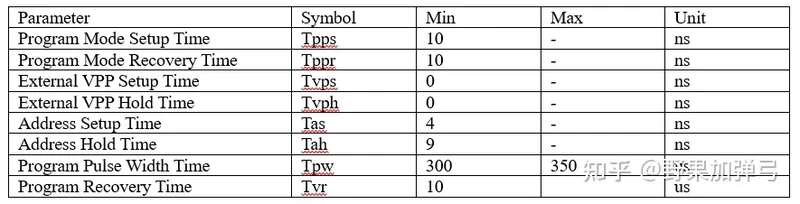

3.4、OTP用户模式写数据时序

依据图 6可知写OTP数据流程的框架和读数据是类似的,都是按照顺序打开电源信号,然后给控制信号,注意写OTP数据需要用到两个电压域信号,先开启VPP引脚5V使能,然后开VDD引脚5V使能,最后开VPP7.5V使能;

关断时先关闭VPP7.5V使能(注意此时VPP引脚的电压为5V),然后关VDD 5V使能,最后关VPP 5V使能。

4、OTP数模接口设计

-

SCLK:时钟接口,ASIC芯片的时钟信号由模拟电路提供。

-

POWOK:模拟给出数字部分的时钟和电源已稳定信号,需要和模拟工程师确认,比如该信号为“1”时是否数字模块的电源和时钟都已稳定,如果不稳定是否需要做debounce(延时),通常该信号和数字电路的异步复位顶层相连。

-

OTPVPP/OTPVDD:OTP IP模块的VPP和VDD电源接口引脚

-

OTPVDDEN:OTP VDD电源使能信号

-

VPP5EN:OTP VPP 电源低压(5V)使能信号

-

VPP7P5EN:OTP VPP 电源高压(7.5V)使能信号

-

REGS_XX:寄存器配置信息,用于模拟电路参数校准

-

SDA/SCL: 低速接口IP PAD信号(如I2C)

注意: OTPVDDEN、VPP5EN和VPP7P5EN是数字电路给模拟电路的电源使能信号,数字电路给出有效电源使能信号后,模拟电路可能需要响应时间,所以这个响应时间应该与模拟工程师确认,只有当OTP的电源信号稳定后才能给出其他的控制信号。

5、OTP仿真模型

P厂商会提供.v 模型文件用于对OTP读写的仿真,OTP模型中,OTPVPP为1表示加高压(7.5V),OTPVPP为0表示普通电压(5V),OTPVDD为“1”表示加普通电压(5V)。所以在利用模型仿真时,关闭电源要用高阻态表示。

wire OTPVDD = OTPVDDEN ? 1’b1 :1’bz

wire OTPVPP = VPP7P5EN ? 1’b1 :(VPP5EN ? 1’b0 :1’bz)

OTP只能烧写一次,用OTP模型进行仿真时会加载一个otp.dat文件其格式如下:

@00000000 ff

@00000001 ff

@00000002 ff

@00000003 ff

@后面的表示地址,ff表示otp的数据,本文举例的OTP默认读出的数值是otp.dat文件中数值的按位取反。

比如@00000000 ff表示的是OTP0地址读出来的数据是00000000,@00000001 fe表示的是OTP1地址读出来的数据是00000001,仿真时,如果手动修改otp.dat的值(将“1”改为“0”)则表示OTP对应的bit已经被修改了。

6、OTP常见功能设计

6.1、OTP上电自动加载数据

由于OTP常常辅助模拟电路进行修调,所以必须要求有OTP上电自动加载功能(OTP地址按0、1、2、3…加载),注意本文提到的OTP在没有烧写时读出的数据全为0,所以寄存器的值应该为其初始值与OTP映射地址值的按位异或:

assign regs_0x01 = auto_load ? 8’h02^otp_wdata:bus_wdata

寄存器regs_0x01的初始值为8’h02,otp_wdata表示数据来自OTP,bus_wdata表示数据来自低速接口,异或逻辑可以保证OTP未烧写时寄存器的初始值不会覆盖,需要注意烧写成自己想要的值时要考虑寄存器初始值和OTP数据按位异或的影响。

譬如regs_0x01初始值为0000_0010,想要将其变为0000_0001,那么OTP的读出值则为0000_0011,那么就需要将该OTP的地址的[1:0]都烧写。

6.2、OTP寄存器操作设计

OTP上电自动加载数据是由硬件产生其读地址和控制信号,搭配低速接口IP,可以通过低速接口对OTP进行读写操作,调试将变得灵活。

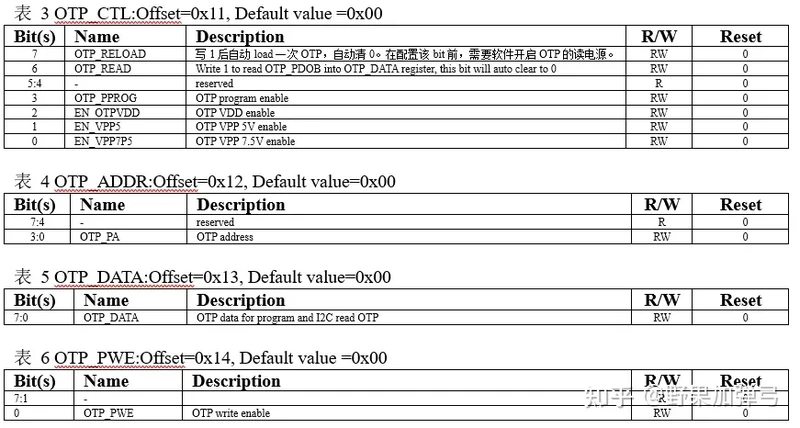

如下4张表格所示定义了OTP的操作寄存器SPEC,通过对寄存器的操作从而完成间接完成对OTP的操作,需要注意的一点是:通过低速接口发出OTP的地址、数据和控制信号同样应该满足OTP时序要求,若低速接口速率太慢则可能不适合用软件的方法去操作OTP。

常用的低速接口如I2C,作slave能支持100K/400K bit/s是可以满足常见OTP的时序要求的。

6.3、OTP分页设计

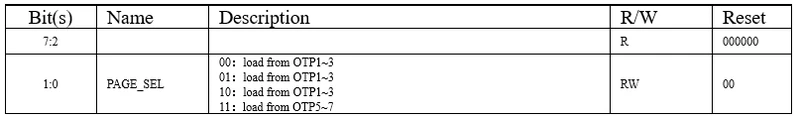

考虑到应用的灵活性,**有时需要对OTP作分页处理。**譬如大小为8X8bit的OTP,将其分为两页,要求能够选择从地址1、2、3还是5、6、7加载数据。

通常做法是将0地址的otp数据作一个判断位。如表 7所示,OTP没有烧写,PAGE_SEL的值为00,此时加载的是OTP1~3的数据,若希望加载OTP5~7的数据则将OTP地址0数据[1:0]烧写为11。

实现方法也很简单,仍然以8X8bit为例子,有如下代码

assign pa = auto_load_flag ? {otp_page_add,auto_load_addr}:reg_otp_pa;

auto_load_addr是otp自动加载数据时的累加地址,

首先加载的是0地址的数据,加载完成后用组合逻辑判断出otp_page_add的值,

如果为0,后续的地址就是1、2、3,

如果otp_page_add的值为1,后续的地址就是5、6、7.

6.4、OTP电源隔离设计

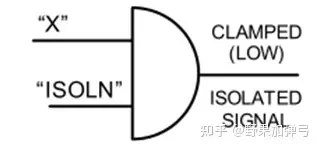

我们知道,在CMOS数字逻辑电路当中,当某根信号为VDD时,我们认为是逻辑1,如果为GND,则认为是逻辑0。但当某块电路不供电后,其输出就失去了驱动,输出网络如果没有其他信号驱动,其电平就会为高阻态,换句话说,就是不知道电压是多少[3]。

因此,如果切断了OTP模块的电源,则OTP的输出就会出现不定值,因此就需要在关断OTP的输出及其连接的模块之间加一个Isolation Cell,在电源关闭时,将OTP的输出固定在某一个电平上,而打开电源后,OTP的输出等于输入,确保正确的数据输出。

对于OTP的输出数据隔离,采用与门即可,直接调用标准单元库的与门逻辑相连即可。

示例代码如下:

AND2X1TAS10 isolation_cell_and2_datao7 (.I1(pdob[7]), .I2(otpvdden), .O(otp_dout[7]));

AND2X1TAS10 isolation_cell_and2_datao6 (.I1(pdob[6]), .I2(otpvdden), .O(otp_dout[6]));

AND2X1TAS10 isolation_cell_and2_datao5 (.I1(pdob[5]), .I2(otpvdden), .O(otp_dout[5]));

AND2X1TAS10 isolation_cell_and2_datao4 (.I1(pdob[4]), .I2(otpvdden), .O(otp_dout[4]));

AND2X1TAS10 isolation_cell_and2_datao3 (.I1(pdob[3]), .I2(otpvdden), .O(otp_dout[3]));

AND2X1TAS10 isolation_cell_and2_datao2 (.I1(pdob[2]), .I2(otpvdden), .O(otp_dout[2]));

AND2X1TAS10 isolation_cell_and2_datao1 (.I1(pdob[1]), .I2(otpvdden), .O(otp_dout[1]));

AND2X1TAS10 isolation_cell_and2_datao0 (.I1(pdob[0]), .I2(otpvdden), .O(otp_dout[0]));

pdob[7:0]是OTP的输出数据,otpvdden是OTP VDD电源控制使能信号,与门逻辑直接调用数字单元库进行例化即可。

参考文献

[1]. 门萌萌. 一种基于CMOS工艺的一次性可编程存储器的研制[D]. 西安电子科技大学, 2016.

[2]. TSMC 0.18um Pure 5V BCD Process 128x8bit One Time Programmable Device Datasheet

[3]. 孙轶群. 数字集成电路低功耗物理实现技术与UPF

[4]. Low Power Methodology Manual For System-on-Chip Design